Toshiba A105 S4064 Maintenance Manual - Page 245

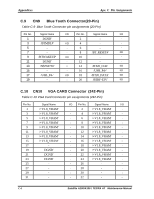

Lcm_3s_vdden, Lcm_ddcpclk_3s

|

UPC - 032017706019

View all Toshiba A105 S4064 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 245 highlights

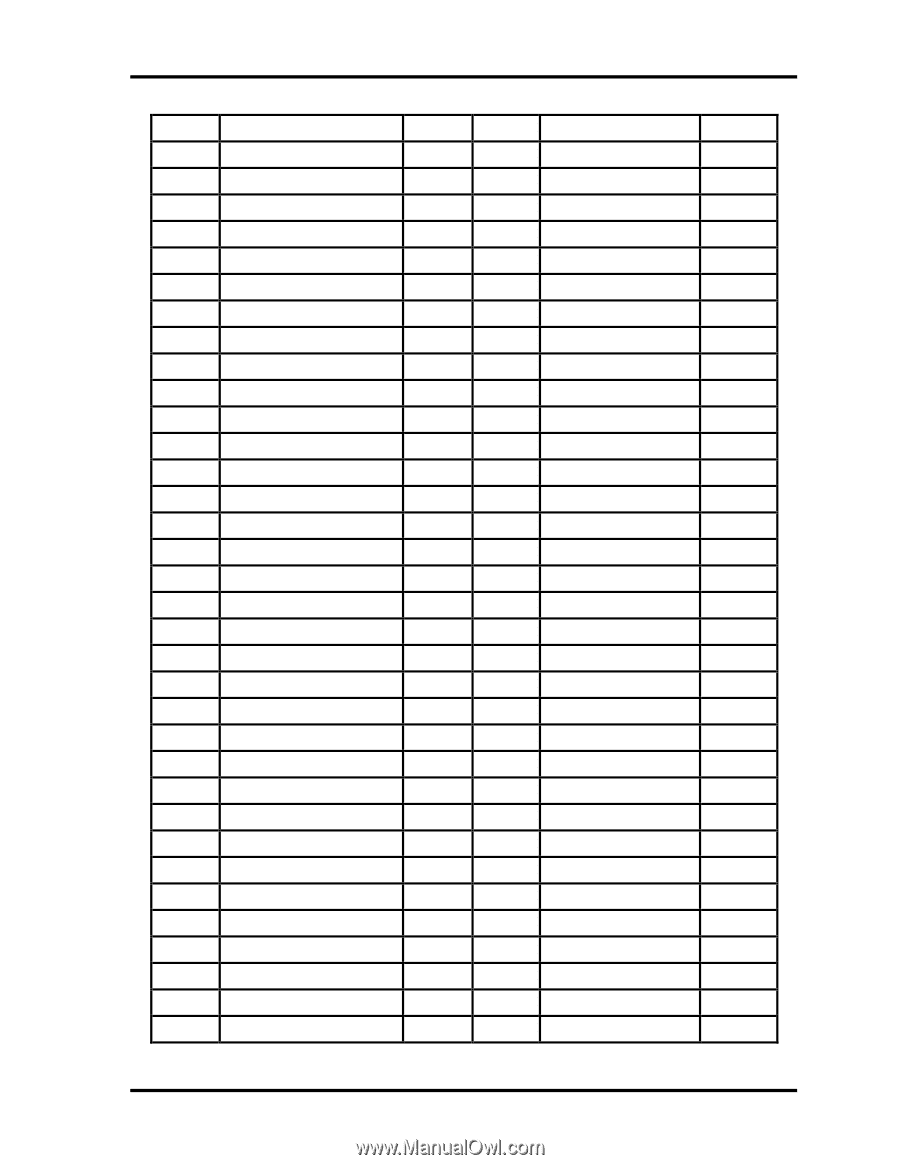

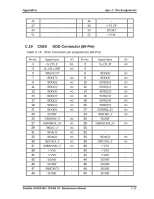

Appendices Apx. C Pin Assignments 173 - - 174 /LVDS_TXDU2-' I/O 175 DGND' - 176 DGND' - 177 - - 178 /LVDS_TXDU0+' I/O 179 - - 180 /LVDS_TXDU0-' I/O 181 DGND' - 182 DGND' - 183 - - 184 /LVDS_TXDU1+' I/O 185 - - 186 /LVDS_TXDU1-' I/O 187 DGND' - 188 DGND' - 189 - - 190 /LVDS_TXDL1+' I/O 191 - - 192 /LVDS_TXDL1-' I/O 193 DGND' - 194 DGND' - 195 - - 196 /LVDS_TXDL0+' I/O 197 - - 198 /LVDS_TXDL0-' I/O 199 DGND' - 200 DGND' - 201 - - 202 /LVDS_TXDL2+' I/O 203 - - 204 /LVDS_TXDL2-' I/O 205 - - 206 DGND' - 207 /CRT_VSYNC' I/O 208 /LVDS_TXCL+' I/O 209 /CRT_HSYNC' I/O 210 /LVDS_TXCL-' I/O 211 /CRT_DDCCLK' I/O 212 DGND' - 213 /CRT_DDCDATA' I/O 214 /CRT_R' I/O 215 /LCM_3S_VDDEN' I/O 216 DGND' - 217 /LCM_3S_BKLTEN' I/O 218 /CRT_G' I/O 219 /INV_PWM_3' I/O 220 DGND' - 221 /LCM_DDCPCLK_3S' I/O 222 /CRT_B' I/O 223 /LCM_DDCPDATA_3S' I/O 224 DGND' - 225 - - 226 /SVID_LUMA' I/O 227 /+V2.5S' - 228 DGND' - 229 /+V2.5S' - 230 /SVID_CHROMA' I/O 231 /+V2.5S' - 232 DGND' - 233 - - 234 - - 235 /+VBAT' - 236 /+VBAT' - 237 /+VBAT' - 238 /+VBAT' - 239 /+VBAT' - 240 /+VBAT' - 241 /+VBAT' - 242 /+VBAT' - Satellite A100/A105 / TECRA A7 Maintenance Manual C-9