Toshiba A105 S4064 Maintenance Manual - Page 262

CN508, DDR2 DIMM1 Socket 200-Pin, M_CLK_DDR1

|

UPC - 032017706019

View all Toshiba A105 S4064 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 262 highlights

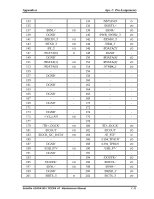

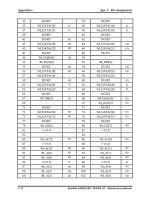

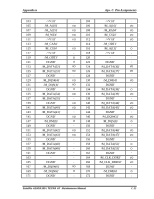

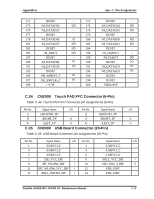

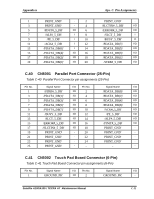

Appendices 173 /M_DATA(50)' 175 /M_DATA(51)' 177 DGND' 179 /M_DATA(56)' 181 /M_DATA(57)' 183 DGND' 185 /M_DM(7)' 187 DGND' 189 /M_DATA(58)' 191 /M_DATA(59)' 193 DGND' 195 /SB_SMDAT_3' 197 /SB_SMCLK_3' 199 /+V3S' I/O 174 I/O 176 - 178 I/O 180 I/O 182 - 184 - 186 - 188 I/O 190 I/O 192 - 194 I/O 196 I/O 198 - 200 Apx. C Pin Assignments /M_DATA(54)' I/O /M_DATA(55)' I/O DGND' - /M_DATA(60)' I/O /M_DATA(61)' I/O DGND' O /M_DQS#(7)' I/O /M_DQS(7)' I/O DGND' - /M_DATA(62)' I/O /M_DATA(63)' I/O DGND' - /N$837418' - /N$837419' - C.33 CN508 DDR2 DIMM1 Socket (200-Pin) Table C-33 DDR2 DIMM1 Socket pin assignments (200-Pin) Pin No. 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 Signal Name /SM_VREF' DGND' /M_DATA(0)' /M_DATA(1)' DGND' /M_DQS#(0)' /M_DQS(0)' DGND' /M_DATA(2)' /M_DATA(3)' DGND' /M_DATA(8)' /M_DATA(9)' DGND' /M_DQS#(1)' I/O Pin No. Signal Name I/O I/O 2 DGND' - - 4 /M_DATA(4)' I I/O 6 /M_DATA(5)' I/O- I/O 8 DGND' - - 10 /M_DM(0)' - O 12 DGND' - I/O 14 /M_DATA(6)' I/O - 16 /M_DATA(7)' - I/O 18 DGND' I/O I/O 20 /M_DATA(12)' I/O - 22 /M_DATA(13)' I/O I/O 24 DGND' - O 26 /M_DM(1)' O - 28 DGND' - I/O 30 /M_CLK_DDR1' I/O C-26 Satellite A100/A105 / TECRA A7 Maintenance Manual