Fujitsu MHT2030AT Manual/User Guide - Page 19

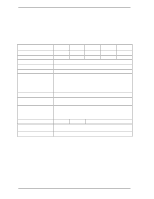

Sustained Ultra DMA data in burst

|

UPC - 683728090579

View all Fujitsu MHT2030AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 19 highlights

Contents Figure 5.4 Protocol for command abort 5-112 Figure 5.5 WRITE SECTOR(S) command protocol 5-114 Figure 5.6 Protocol for the command execution without data transfer ...........5-115 Figure 5.7 Normal DMA data transfer 5-117 Figure 5.8 Ultra DMA termination with pull-up or pull-down 5-129 Figure 5.9 PIO data transfer timing 5-130 Figure 5.10 Multiword DMA data transfer timing (mode 2 5-131 Figure 5.11 Initiating an Ultra DMA data in burst 5-132 Figure 5.12 Sustained Ultra DMA data in burst 5-136 Figure 5.13 Host pausing an Ultra DMA data in burst 5-137 Figure 5.14 Device terminating an Ultra DMA data in burst 5-138 Figure 5.15 Host terminating an Ultra DMA data in burst 5-139 Figure 5.16 Initiating an Ultra DMA data out burst 5-140 Figure 5.17 Sustained Ultra DMA data out burst 5-141 Figure 5.18 Device pausing an Ultra DMA data out burst 5-142 Figure 5.19 Host terminating an Ultra DMA data out burst 5-143 Figure 5.20 Device terminating an Ultra DMA data out burst 5-144 Figure 5.21 Power-on Reset Timing 5-145 Figure 6.1 Figure 6.2 Figure 6.3 Figure 6.4 Figure 6.5 Figure 6.6 Figure 6.7 Response to power-on 6-3 Response to hardware reset 6-4 Response to software reset 6-5 Response to diagnostic command 6-6 Sector slip processing 6-10 Automatic alternating processing 6-11 Data buffer structure 6-12 C141-E192-02EN xv