Fujitsu MHT2030AT Manual/User Guide - Page 37

System Configuration, 2.2.1 ATA interface, 2.2.2 1 drive connection - connector

|

UPC - 683728090579

View all Fujitsu MHT2030AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

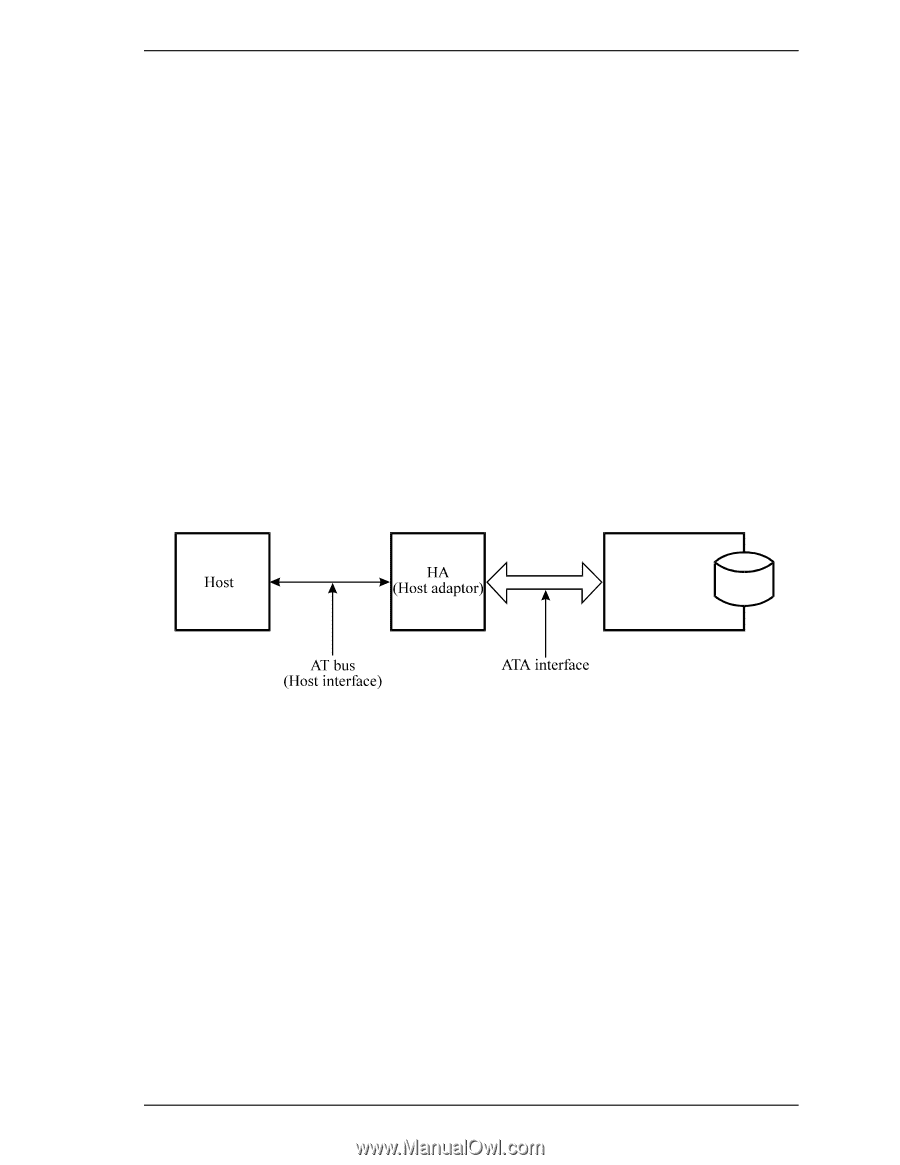

2.2 System Configuration (6) Read/write circuit The read/write circuit uses a LSI chip for the read/write preamplifier. It improves data reliability by preventing errors caused by external noise. (7) Controller circuit The controller circuit consists of an LSI chip to improve reliability. The highspeed microprocessor unit (MPU) achieves a high-performance AT controller. 2.2 System Configuration 2.2.1 ATA interface Figures 2.2 and 2.3 show the ATA interface system configuration. The drive has a 44pin PC AT interface connector and supports PIO mode 4 transfer at 16.6 MB/s, Multiword DMA mode 2 transfer at 16.6 MB/s and also U-DMA mode 5 (100 MB/s). 2.2.2 1 drive connection MHT2080AT MMHHTC22006302AATT MMHHTC22004400AATT MHT2030AT Figure 2.2 1 drive system configuration C141-E192-02EN 2-3