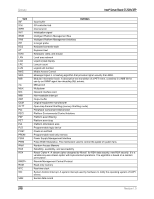

Intel S1200RP Technical Product Specification - Page 259

Glossary

|

View all Intel S1200RP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 259 highlights

Intel® Server Board S1200V3RP Glossary Glossary This appendix contains important terms used in the preceding chapters. For ease of use, numeric entries are listed first (for example, "82460GX") with alpha entries following (for example, "AGP 4x"). Acronyms are then entered in their respective place, with non-acronyms following. Term ACPI AES AMB APIC ARP ASF ASIC BIST BMC Bridge BSP CBC CLI CLTT CMOS CSR D-cache DHCP DIB DPC EEPROM EMP EPS FML FNI FRB FRU FSB FTM GPIO HSBP HSC I-cache I2C IA Definition Advanced Configuration and Power Interface Advanced Encryption Standard Advanced Memory Buffer (there is an AMB on each FBDIMM) Advanced Programmable Interrupt Controller Address Resolution Protocol Alert Standards Forum Application specific integrated circuit Built-in self test Baseboard management controller Circuitry connecting one computer bus to another, allowing an agent on one to access the other. Bootstrap processor Chassis bridge controller. A microcontroller connected to one or more other CBCs. Together they bridge the IPMB buses of multiple chassis. Command-line interface Closed-loop thermal throttling (memory throttling mode) In terms of this specification, this describes the PC-AT compatible region of battery-backed 128 bytes of memory on the server board. Control and status register Data cache. Processor-local cache dedicated for memory locations explicitly loaded and stored by running code. Dynamic Host Configuration Protocol Device Information Block Direct Platform Control Electrically erasable programmable read-only memory Emergency management port External Product Specification Fast management link Fast management link network interface Fault resilient booting Field replaceable unit Front side bus Firmware transfer mode General-purpose input/output Hot-swap backplane Hot-swap controller Instruction cache. Processor-local cache dedicated for memory locations retrieved through instruction fetch operations. Inter-integrated circuit bus Intel® architecture Revision 1.0 247