Intel E6600 Specification Update - Page 11

Errata, M0

|

UPC - 735858184625

View all Intel E6600 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 11 highlights

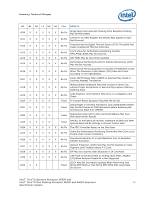

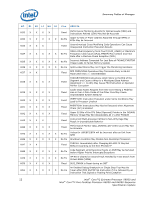

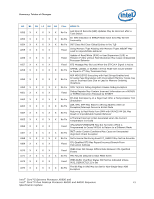

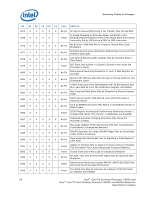

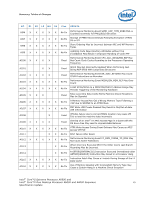

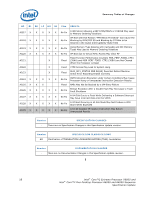

Summary Tables of Changes NO B1 B2 L2 M0 G0 Plan ERRATA AI10 X X X X X No Fix Single Step Interrupts with Floating Point Exception Pending May Be Mishandled AI11 X X X X X No Fix A Write to an APIC Register Sometimes May Appear to Have Not Occurred AI12 X X X X X No Fix Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts AI13 X X X X X No Fix Count Value for Performance-Monitoring Counter PMH_PAGE_WALK May be Incorrect AI14 X X X X X No Fix LER MSRs May be Incorrectly Updated AI15 X X X X X No Fix Performance Monitoring Events for Retired Instructions (C0H) May Not Be Accurate Performance Monitoring Event For Number Of Reference Cycles AI16 X X X X X No Fix When The Processor Is Not Halted (3CH) Does Not Count According To The Specification AI17 X X X X X No Fix Using 2M/4M Pages When A20M# Is Asserted May Result in Incorrect Address Translations Writing Shared Unaligned Data that Crosses a Cache Line AI18 X X X X X No Fix without Proper Semaphores or Barriers May Expose a Memory Ordering Issue AI19 X X X X X No Fix Code Segment Limit Violation May Occur on 4 Gigabyte Limit Check AI20 X X X X Fixed FP Inexact-Result Exception Flag May Not Be Set AI21 X X X X Fixed Global Pages in the Data Translation Look-Aside Buffer (DTLB) May Not Be Flushed by RSM instruction before Restoring the Architectural State from SMRAM AI22 X X X X Fixed Sequential Code Fetch to Non-canonical Address May have Non-deterministic Results AI23 X X X X Fixed VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field AI24 X X X X X No Fix The PECI Controller Resets to the Idle State AI25 X X X X X No Fix Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions AI26 X X X X X No Fix Premature Execution of a Load Operation Prior to Exception Handler Invocation AI27 X X X X X No Fix General Protection (#GP) Fault May Not Be Signaled on Data Segment Limit Violation above 4-G Limit AI28 X X X X X No Fix EIP May be Incorrect after Shutdown in IA-32e Mode AI29 X X X X X No Fix #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported AI30 X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification Update