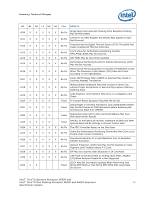

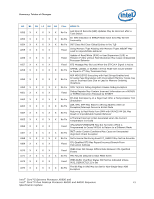

Summary Tables of Changes

12

Intel

®

Core™2 Extreme Processor X6800 and

Intel

®

Core™2 Duo Desktop Processor E6000 and E4000 Sequence

Specification Update

NO

B1

B2

L2

M0

G0

Plan

ERRATA

AI31

X

X

X

X

Fixed

Performance Monitoring Events for Retired Loads (CBH) and

Instructions Retired (C0H) May Not Be Accurate

AI32

X

X

X

X

X

No Fix

Upper 32 bits of 'From' Address Reported through BTMs or

BTSs May be Incorrect

AI33

X

X

X

Fixed

Unsynchronized Cross-Modifying Code Operations Can Cause

Unexpected Instruction Execution Results

AI34

X

X

X

X

X

No Fix

MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum

Frequency Clock Count (IA32_MPERF) May Contain Incorrect

Data after a Machine Check Exception (MCE)

AI35

X

X

X

X

X

No Fix

Incorrect Address Computed For Last Byte of FXSAVE/FXRSTOR

Image Leads to Partial Memory Update

AI36

X

X

X

X

X

No Fix

Split Locked Stores May not Trigger the Monitoring Hardware

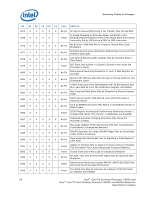

AI37

X

X

Fixed

REP CMPS/SCAS Operations May Terminate Early in 64-bit

Mode when RCX >= 0X100000000

AI38

X

X

X

X

Fixed

FXSAVE/FXRSTOR Instructions which Store to the End of the

Segment and Cause a Wrap to a Misaligned Base Address

(Alignment <= 0x10h) May Cause FPU Instruction or Operand

Pointer Corruption

AI39

X

X

X

X

Fixed

Cache Data Access Request from One Core Hitting a Modified

Line in the L1 Data Cache of the Other Core May Cause

Unpredictable System Behavior

AI40

X

X

X

X

Fixed

PREFETCHh Instruction Execution under Some Conditions May

Lead to Processor Livelock

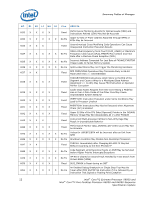

AI41

X

X

X

X

Fixed

PREFETCHh Instructions May Not be Executed when Alignment

Check (AC) is Enabled

AI42

X

X

X

X

Fixed

Upper 32 Bits of the FPU Data (Operand) Pointer in the FXSAVE

Memory Image May Be Unexpectedly All 1's after FXSAVE

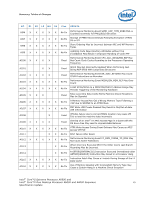

AI43

X

X

X

Fixed

Concurrent Multi-processor Writes to Non-dirty Page May

Result in Unpredictable Behavior

AI44

X

X

X

X

Fixed

Performance Monitor IDLE_DURING_DIV (18h) Count May Not

be Accurate

AI45

X

X

X

X

X

No Fix

Values for LBR/BTS/BTM will be Incorrect after an Exit from

SMM

AI46

X

X

X

X

X

No Fix

Shutdown Condition May Disable Non-Bootstrap Processors

AI47

X

X

Fixed

SYSCALL Immediately after Changing EFLAGS.TF May Not

Behave According to the New EFLAGS.TF

AI48

X

X

X

X

X

No Fix

Code Segment Limit/Canonical Faults on RSM May be Serviced

before Higher Priority Interrupts/Exceptions

AI49

X

X

X

X

X

No Fix

VM Bit is Cleared on Second Fault Handled by Task Switch from

Virtual-8086 (VM86)

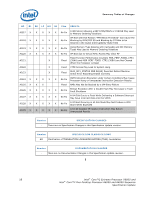

AI50

X

X

X

X

Fixed

IA32_FMASK is Reset during an INIT

AI51

X

X

X

X

X

No Fix

An Enabled Debug Breakpoint or Single Step Trap May Be

Taken after MOV SS/POP SS Instruction if it is Followed by an

Instruction That Signals a Floating Point Exception