Intel Q9400S Data Sheet - Page 91

Deep Sleep State, Deeper Sleep State

|

UPC - 735858207973

View all Intel Q9400S manuals

Add to My Manuals

Save this manual to your list of manuals |

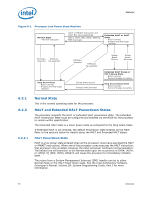

Page 91 highlights

Features 6.2.6 6.2.7 state. Snoop events that occur while in Sleep state or during a transition into or out of Sleep state will cause unpredictable behavior. Any transition on an input signal before the processor has returned to the Stop-Grant state will result in unpredictable behavior. If RESET# is driven active while the processor is in the Sleep state, and held active as specified in the RESET# pin specification, then the processor will reset itself, ignoring the transition through the Stop-Grant state. If RESET# is driven active while the processor is in the Sleep state, the SLP# and STPCLK# signals should be deasserted immediately after RESET# is asserted to ensure the processor correctly executes the Reset sequence. While in the Sleep state, the processor is capable of entering an even lower power state, the Deep Sleep state, by asserting the DPSLP# pin (See Section 6.2.6). While the processor is in the Sleep state, the SLP# pin must be deasserted if another asynchronous FSB event needs to occur. PECI is not available and will not respond while in the Sleep State. Deep Sleep State The Deep Sleep state is entered through assertion of the DPSLP# pin while in the Sleep state. BCLK may be stopped during the Deep Sleep state for additional platform level power savings. BCLK stop/restart timings on appropriate chipset-based platforms with the CK505 clock chip are as follows: • Deep Sleep entry: the system clock chip may stop/tristate BCLK within two BCLKs of DPSLP# assertion. It is permissible to leave BCLK running during Deep Sleep. • Deep Sleep exit: the system clock chip must drive BCLK to differential DC levels within 2-3 ns of DPSLP# de-assertion and start toggling BCLK within 10 BCLK periods. To re-enter the Sleep state, the DPSLP# pin must be deasserted. BCLK can be restarted after DPSLP# de-assertion as described above. A period of 15 microseconds (to allow for PLL stabilization) must occur before the processor can be considered to be in the Sleep state. Once in the Sleep state, the SLP# pin must be deasserted to re-enter the Stop-Grant state. While in the Deep Sleep state the processor is incapable of responding to snoop transactions or latching interrupt signals. No transitions of signals are allowed on the FSB while the processor is in the Deep Sleep state. When the processor is in the Deep Sleep state it will not respond to interrupts or snoop transactions. Any transition on an input signal before the processor has returned to the Stop-Grant state will result in unpredictable behavior. PECI is not available and will not respond while in the Deep Sleep State. Deeper Sleep State The Deeper Sleep state is similar to the Deep Sleep state but the core voltage is reduced to a lower level. The Deeper Sleep state is entered through assertion of the DPRSTP# pin while in the Deep Sleep state. Exit from Deeper Sleep is initiated by DPRSTP# de-assertion. PECI is not available and will not respond while in the Deeper Sleep State. Datasheet 93