Asus P I-P55SP3AV P/I-P55SP3AV User's manual - Page 80

Asus P I-P55SP3AV Manual

|

View all Asus P I-P55SP3AV manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 80 highlights

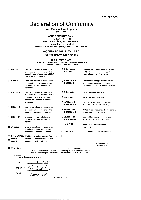

TECHNICAL UPDATE Product Number: Motherboard Revision: Manual Revision: P/I-P55SP3AV 1.2 and later 1.02 On page 1-4, the forth feature item should read: • Write-back "Level 2" external static RAM cache with two cache options, SRAM sockets and a cache module slot. The SRAM socket allows installation of 256KB, 512KB, or 1MB of SRAM cache chips. When a pipeline burst cache module is installed you must remove the SRAM chips to prevent conflicts. • On page 1-5, the third feature item second sentence should read: ...The controller supports PIO Modes 3 and 4 at a maximum transfer rate of 17MB/second and Bus Master IDE DMA Mode 2 at maximum transfer rate of 22MB/second. On page 4-6, remove all references to 40MHz Ext. Clock On page 4-11, the Fan power connector in detail: JP 17 GND +12V GND CPU Fan Power Connector r cchnical U )date P/I-P55SP3AV User's Manual