Foxconn MARS English Manual. - Page 47

Memory Timing Config

|

View all Foxconn MARS manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 47 highlights

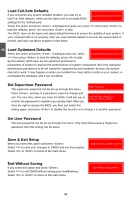

3 CPUID MaxVal to 3. Should be [Disabled] for WinXP. ► C1E Function C1E represents Enhanced HALT State. It is a feature which Intel CPU uses to reduce power consumption when in halt state. C1E drops the CPU's multiplier and voltage to lower levels when a HLT (halt) command is issued. This item is used to enable/disable the C1E support. ► Execute Disable Bit This item is used to enable/disable the Execute Disable Bit feature. Intel's Execute Disable Bit functionality can help prevent certain classes of malicious buffer overflow attacks when combined with a supporting operating system. Execute Disable Bit allows the processor to classify areas in memory by where application code can execute and where it cannot. When a malicious worm attempts to insert code in the buffer, the processor disables code execution, preventing damage and worm propagation. Replacing older computers with Execute Disable Bit-enabled systems can halt worm attacks, reducing the need for virus-related repairs. By combining Execute Disable Bit with anti-virus, firewall, spyware removal, e-mail filtering software, and other network security measures, IT managers can free IT resources for other initiatives. ► Frequency Unlimit It means the processor is not ratio locked and has no factory configured maximum ratio limit on the Smithfield XE multi-processing CPU core. ► Core Multi-Processing When disabled, it will disable one execution core of each CPU die. It is going to provide backward compatibility, any way, keep it enabled. ► Virtualization Technology Virtualization (i.e. Intel® Vanderpool Technology) allows a platform to run multiple operating systems and applications in independent partitions or "containers." One physical compute system can function as multiple "virtual" systems. Vanderpool Technology can help improve future virtualization solutions. This item will be displayed only when the CPU is supporting this feature and the setting is used to enable/disable it. Memory Timing Config Phoenix - AwardBIOS CMOS Setup Utility Memory Timing Config DRAM Timing Selectable By SPD Item Help CAS Latency Time (tCL) Auto RAS# to CAS# Delay (tRCD) Auto Menu Level ► RAS# Precharge (tRP) Auto Prechange delay (tRAS) Auto Write to Precharge(tWR) Auto Row Refresh Cycle(tRFC) Auto Write to Read Delay(tWTR) Auto Row to Row Delay(tRRD) Auto Read to Precharge(tRPT) Auto Fast Chip Select Auto Clock Per Command Auto Memory Channel0 DLL Adjust Auto Memory Channel1 DLL Adjust Auto Refresh Count Adjust Auto Performance Level Auto Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help F5:Previous Values F6:Fail-Safe Defaults F7:Optimized Defaults 40