Intel SE7505VB2 Product Specification - Page 26

Compatibility Interrupt Control, APIC, General Purpose Input and Output Pins, Functional Architecture

|

View all Intel SE7505VB2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 26 highlights

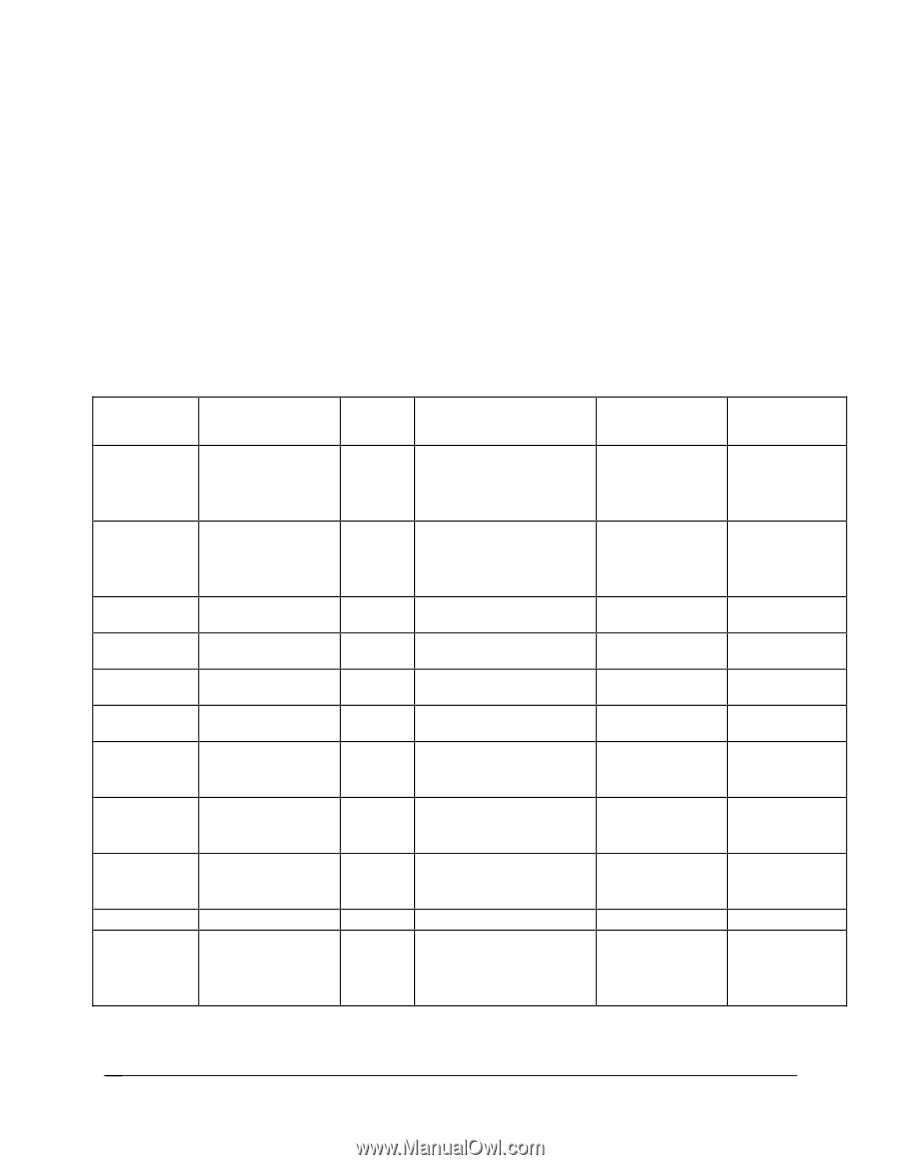

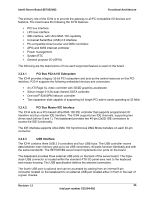

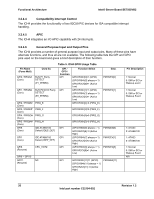

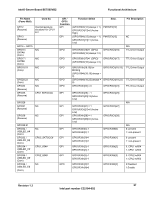

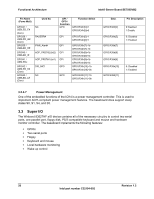

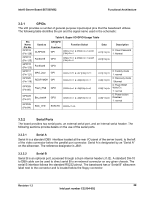

Functional Architecture Intel® Server Board SE7505VB2 3.2.4.4 Compatibility Interrupt Control The ICH4 provides the functionality of two 82C59 PIC devices for ISA-compatible interrupt handling. 3.2.4.5 APIC The ICH4 integrates an I/O APIC capability with 24 interrupts. 3.2.4.6 General Purpose Input and Output Pins The ICH4 provides a number of general purpose input and output pins. Many of these pins have alternate functions, and thus all are not available. The following table lists the GPI and GPO pins used on the board and gives a brief description of their function. Table 5. ICH4 GPIO Usage Table Pin Name (Powe Well) Used As GPI0 / REQA# (Core) BUS P1 Parity DETECT (P1_PERR#) GPI1 / REQB# (Core) BUS P2/ICH4 Parity DETECT (P2_PERR#) GPI2 / PIRQE# (Core) GPI3 / PIRQF# (Core) GPI4 / PIRQG# (Core) GPI5 / PIRQH# (Core) GPI6 (Core) PIRQ_E PIRQ_F PIRQ_G PIRQ_H IDE ATA66/100 Detect (IDES_DET) GPI7 (Core) IDE ATA66/100 Detect (IDEP_DET) GPI8 (Resume) CPU_HOT# GPI9 ~ GPI10 GPI11 NC (Resume) GPI / GPO / Function GPI GPI Function Select GPIO:R00h[0]=1 (GPIO) (GPIO:R04h[0] always = 1) GPIO:R2Ch[0]=1 (Active Low) GPIO:R00h[1]=1 (GPIO) (GPIO:R04h[1] always = 1) GPIO:R2Ch[1]=1 (Active Low) GPIO:R00h[2]=0 (PIRQ_E) Data. PM:R2Eh[0] PM:R2Eh[1] GPIO:R00h[3]=0 (PIRQ_F) GPIO:R00h[4]=0 (PIRQ_G) GPIO:R00h[5]=0 (PIRQ_H) GPI (GPIO:R04h[6] always = 1) PM:R2Eh[6] GPIO:R2Ch[6]=0 (Active High) GPI (GPIO:R04h[7] always = 1) PM:R2Eh[7] GPIO:R2Ch[7]=0 (Active High) GPI (GPIO:R04h[8] always = 1) PM:R2Eh[8] GPIO:R2Ch[8]=1 (Active Low) GPI GPIO:R00h[11]=1 (GPIO) PM:R2Eh[11] (GPIO:R04h[11] always = 1) GPIO:R2Ch[11]=0 (Active High) Pin Description 1: Normal 0: SMI or SCI or Wakeup event 1: Normal 0: SMI or SCI or Wakeup Event 1: ATA33 0: ATA66/100 1: ATA33 0: ATA66/100 1: Normal 0: SMI or SCI or Wakeup Event N/A 26 Revision 1.2 Intel part number C32194-002