Foxconn FlamingBlade GTI English Manual. - Page 52

► tRCD RAS to CAS Delay

|

View all Foxconn FlamingBlade GTI manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

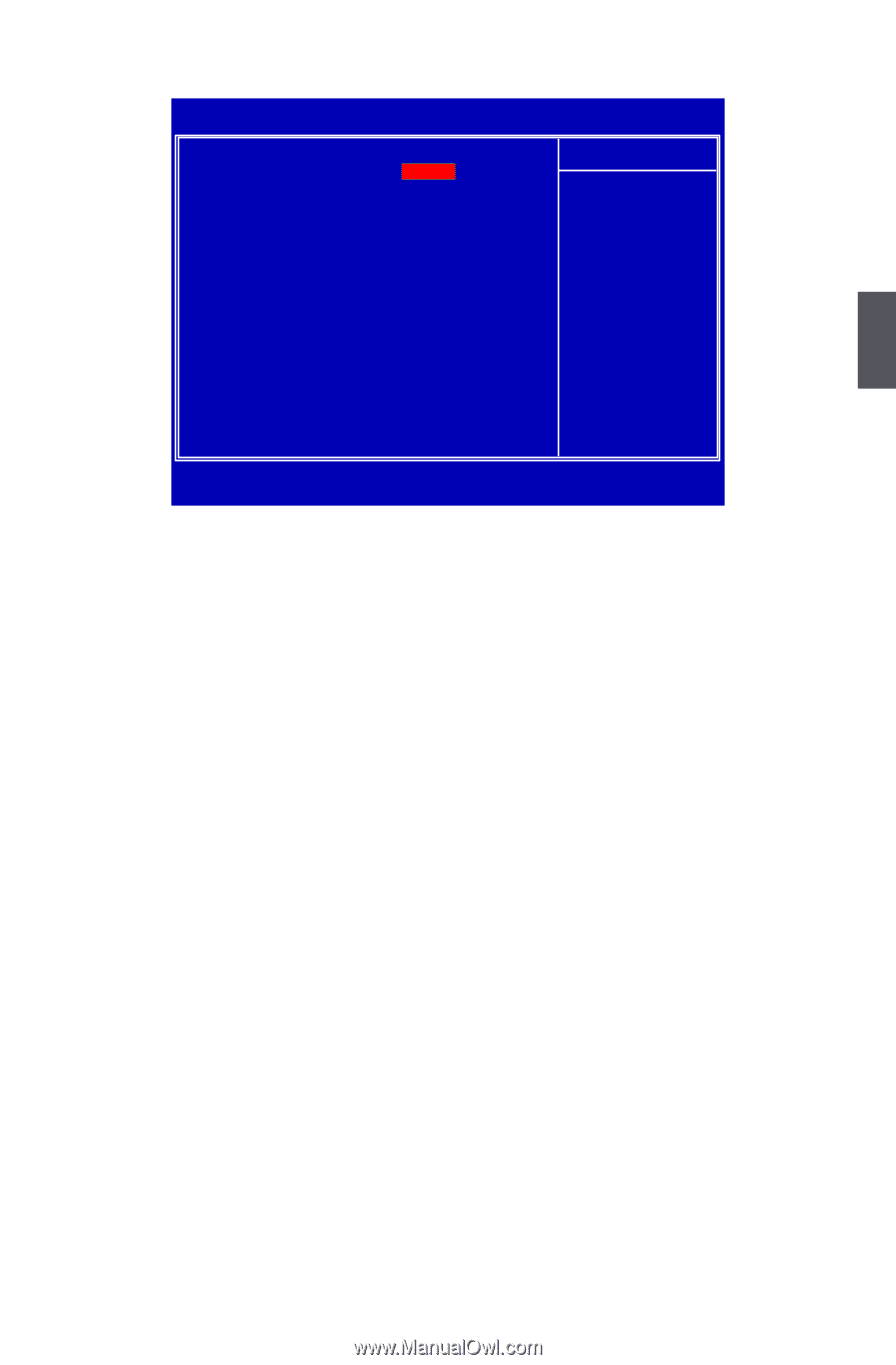

Memory Settings Phoenix - AwardBIOS CMOS Setup Utility Memory Settings ******** Memory Controller Settings ******** Item Help IMC Configuration Enabled Channel Configuration Independent Menu Level ► Channel Interleaving 6 way Rank Interleaving 4 way Memory Timings Virtual XMP Disabled x DRAM Timing Control By SPD x tCL (CAS Latency) Auto x tRCD (RAS to CAS Delay) Auto x tRP (RAS Precharge) Auto x tRAS (Precharge Delay) Auto x CR (Command Rate) Auto x tRFC (Refresh Cycle Time) Auto x tWR (Write Recovery Time) Auto x tWTR (Write to Read Delay) Auto x tRRD (RAS to RAS Delay) Auto x tRTP (Read to Precharge) Auto 3 Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help F5:Previous Values F7:Optimized Defaults ► IMC Configuration This item is used to enable or disable memory parameter settings. ► Channel Configuration Options are: Independent, Mirror, Lock, Spare. ► Channel Interleaving This item is used to set Max. DRAM channel interleave. Options are: from 1 way to 6 way. ► Rank Interleaving Interleaving allows banks of SDRAM to alternate their refresh and access cycles. One bank will undergo its refresh cycle while another is being accessed. This improves memory performance by masking the refresh cycles of each memory bank. However, bank interleaving only works if the addresses requested consecutively are not in the same bank. Option are: 1 way, 2 way and 4 way. ► Virtual XMP Intel XMP is a performance-packed expansion of the standard DDR3 memory specification, enabling a robust, overclocking solution designed to take advantage of the mega-gaming features built into Intel® technology-based PCs. If you like to overclock and squeeze every possible ounce of performance from your PC, then memory based on Intel XMP is the solution you need to destroy your enemies and save the universe without breaking a sweat. This item is used to enable or disable Intel XMP. ► tCL (CAS Latency) This item controls the CAS latency, which determines the timing delay (in clock cycles) before SDRAM starts a read command after receiving it. ► tRCD (RAS to CAS Delay) This item allows you to select a delay time (in clock cycles) between the CAS and RAS strobe signals. ► tRP (RAS Precharge) This item allows you to select the DRAM RAS precharge time (in clock cycles). ► tRAS (Precharge Delay) This item allows you to set the precharge delay time (in clock cycles). 45