HP ProLiant DL980 DL980 G7 Maintenance & Service Guide - Page 45

Hemisphere mode, Memory performance optimization

|

View all HP ProLiant DL980 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 45 highlights

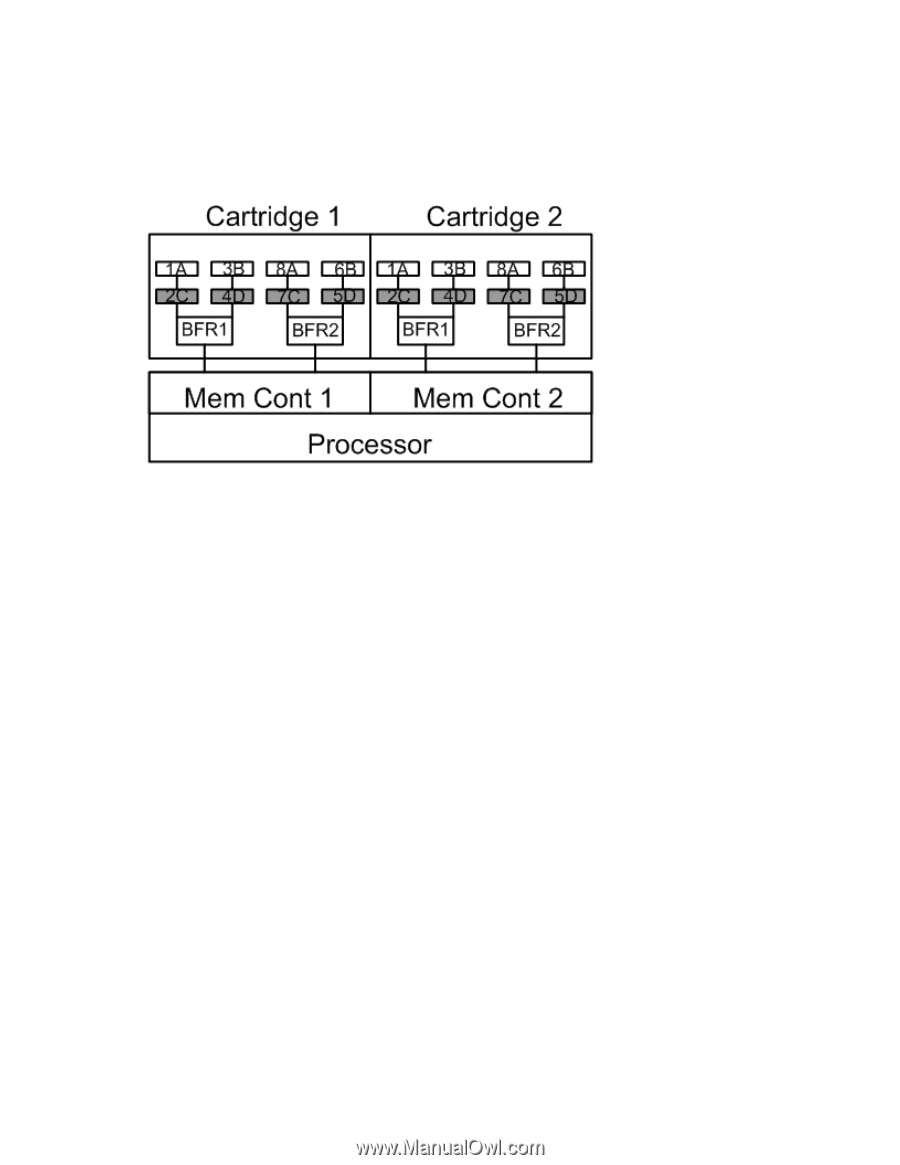

• Successive cache lines are interleaved between the DIMMs and the Lockstep SMI channels of the two memory controllers in the processor such that adjacent cache lines reside on different memory controllers, SMIs, DIMMs, and DIMM ranks for better performance. To take advantage of this feature, DIMMs should be populated evenly between all SMI channels. If an SMI channel pair has more DIMMs than others, the extra memory on that SMI channel pair does not benefit from the interleaving mechanism across memory controllers. Hemisphere mode The Intel® Xeon™ 7500-series processor architecture incorporates Hemisphere mode, a high-performance interleaving technology. Hemisphere mode combines the tracking resources of both memory controllers within each processor for a more aggressive cache line pipelining. Hemisphere mode is the only supported configuration, and is enabled in RBSU when processors in the system have identical DIMM population behind both of their memory controllers. That is to say, all populated memory cartridges are populated the same way. • Hemisphere mode should produce the best overall performance for a variety of applications. • To enable each processor to enter Hemisphere mode, both memory cartridges must be installed and populated with equal memory capacities based on the DIMM installation guidelines (on page 43). • Greater performance is obtained when all cartridges are populated with either four or eight dual- or quad-rank DIMMs. • The server supports Mirrored Memory mode while Hemisphere mode is enabled. Memory performance optimization The server supports 128 DIMMS across eight Multi-core processors (64 DIMMs across four multi-core processors, in each processor memory drawer). While there are many DIMM population configurations that can support any total memory size, optimal performance is achieved when populated DIMMs can take advantage of the Intel® Xeon™ 7500-series processor architecture. To achieve the best performance for a given memory processor configuration, observe the following guidelines: • The largest contributor to maximum memory bandwidth performance is to use both memory controllers inside the processor. To achieve maximum memory bandwidth performance, populate both memory cartridges for each installed processor. This configuration is required for this server. Illustrated parts catalog 45