Intel D845PEBT2 Product Specification - Page 124

Intel Desktop Board D845PEBT2 Technical Product Specification, Description of POST Operation

|

View all Intel D845PEBT2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 124 highlights

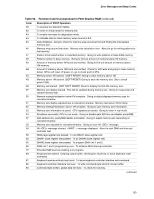

Intel Desktop Board D845PEBT2 Technical Product Specification Table 92. Runtime Code Uncompressed in F000 Shadow RAM (continued) Code 84 85 86 87 88 89 8B 8C 8D 8F 91 95 96 97 98 99 9A 9B 9C 9D 9E A2 A3 A4 A5 A7 A8 A9 AA AB AC AD Description of POST Operation Lock-key checking over. To check for memory size mismatch with CMOS. Memory size check done. To display soft error and check for password or bypass setup. Password checked. About to do programming before setup. Programming before setup complete. To uncompress SETUP code and execute CMOS setup. Returned from CMOS setup program and screen is cleared. About to do programming after setup. Programming after setup complete. Going to display power-on screen message. First screen message displayed. message displayed. PS/2 Mouse check and extended BIOS data area allocation to be done. Setup options programming after CMOS setup about to start. Going for hard disk controller reset. Hard disk controller reset done. Floppy setup to be done next. Floppy setup complete. Hard disk setup to be done next. Init of different buses optional ROMs from C800 to start. (See Section 5.3 for details of different buses.) Going to do any init before C800 optional ROM control. Any init before C800 optional ROM control is over. Optional ROM check and control will be done next. Optional ROM control is done. About to give control to do any required processing after optional ROM returns control and enable external cache. Any initialization required after optional ROM test over. Going to setup timer data area and printer base address. Return after setting timer and printer base address. Going to set the RS-232 base address. Returned after RS-232 base address. Going to do any initialization before Coprocessor test. Required initialization before Coprocessor is over. Going to initialize the Coprocessor next. Coprocessor initialized. Going to do any initialization after Coprocessor test. Initialization after Coprocessor test is complete. Going to check extended keyboard, keyboard ID and num-lock. Going to display any soft errors. Soft error display complete. Going to set keyboard typematic rate. Keyboard typematic rate set. To program memory wait states. Going to enable parity/NMI. NMI and parity enabled. Going to do any initialization required before giving control to optional ROM at E000. Initialization before E000 ROM control over. E000 ROM to get control next. Returned from E000 ROM control. Going to do any initialization required after E000 optional ROM control. Initialization after E000 optional ROM control is over. Going to display the system configuration. Put INT13 module runtime image to shadow. Generate MP for multiprocessor support (if present). Put CGA INT10 module (if present) in Shadow. continued 124