Epson ActionTower 3000 User Manual - Page 107

MB, 8MB, 16MB, and 32MB SIMMs, to 64MB using 1MB, 2MB

|

View all Epson ActionTower 3000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 107 highlights

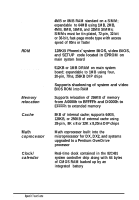

Memory ROM video RAM Shadow RAM Memory relocation Cache Math coprocessor Clock/ calendar 4MB or 8MB RAM standard on a SIMM; expandable to 64MB using 1MB, 2MB, 4MB, 8MB, 16MB, and 32MB SIMMs; SIMMs must be tin-plated, 72-pin, 32-bit or 36-bit, fast-page mode type with access speed of 80ns or faster 128KB Phoenix® system BIOS, video BIOS, and SETUP code located in EPROM on main system board 512KB or 1MB DRAM on main system board; expandable to 1MB using four, 20-pin, 70ns, 256KB DIP chips Supports shadowing of system and video BIOS ROM into RAM Supports relocation of 256KB of memory from A0000h to BFFFFh and D0000h to EFFFFh to extended memory 8KB of internal cache; supports 64KB, 128KB, or 256KB of external cache using 28-pin, 8K x 8 or 32K x 8,20ns DIP chips Math coprocessor built into the microprocessor for DX, DX2, and systems upgraded to a Pentium OverDrive processor Real-time clock contained in the 82C491 system controller chip along with 64 bytes of CMOS RAM backed up by an integrated battery A - 2 Specifications