Acer Aspire 6530G Aspire 6530/6530G Quick Guide - Page 145

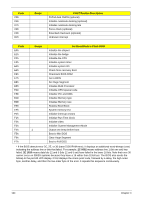

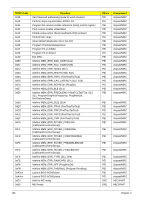

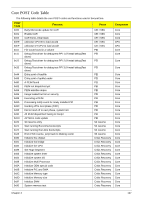

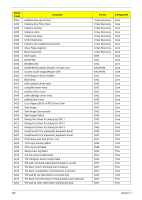

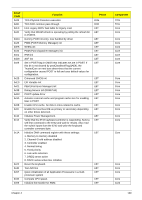

Chipset POST Codes, POST Code, Function, Phase, Component

|

View all Acer Aspire 6530G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 145 highlights

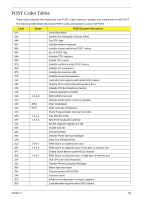

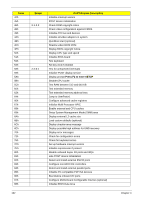

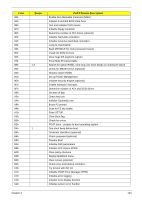

Chipset POST Codes The following table details the Chipset POST codes and components used in the POST. POST Code 0xA0 0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08 0x09 0x10 0x11 0x12 0x13 0x14 0x17 0x18 0x19 0x20 0x21 0x22 0x23 0x24 0x25 0x26 0x27 0x28 0x29 0x30 0x31 0x32 0x33 0x34 0x35 0x36 0x37 0x38 Function MRC Entry Enable MCHBAR Check ME existence Check for DRAM initialization interrupt and reset fail Determine the system Memory type based on first populated socket Verify all DIMMs are DDR2 and SO-DIMMS, which are unbuffered Verify all DIMMs are Non-ECC Verify all DIMMs are single or double sided and not mixed Verify all DIMMs are x8 or x16 width Calculate number of Row and Column bits Calculate number of banks for each DIMM Determine raw card type Find a common CAS latency between the DIMMS and the MCH Determine the memory frequency and CAS latency to program Determine the smallest common timing value for all DIMMS Power management resume Program DRAM type (DDR2/DDR3) and Power up sequence Program the correct system memory frequency Program the correct Graphics memory frequency Early DRC initialization Program the DRAM Row Attributes and DRAM Row Boundary registers PRE JEDEC. Program the RCOMP SRAM registers Program DRAM type (DDR2/DDR3) and Power up sequence Program the DRAM Timing Program the DRAM Bank Architecture register Enable all clocks on populated rows Program MCH ODT Program tRD Miscellaneous Pre JEDEC steps Program clock crossing registers Program the Egress port timings Program the Memory IO registers Perform steps required before JEDEC Perform JEDEC memory initialization for all memory rows Setup DRAM control register for normal operation and enable Do ZQ calibration for DDR3 Perform final Dra/Drb programming, Set the mode of operation for the memory channels Phase PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI Component chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC Chapter 4 135