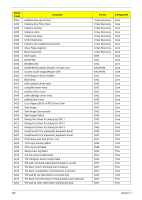

Acer Aspire 6530G Aspire 6530/6530G Quick Guide - Page 150

Initialize Extended BIOS Data Area and initialize the mouse., Install the IRQ vectors Sever Hotkey

|

View all Acer Aspire 6530G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 150 highlights

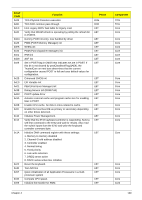

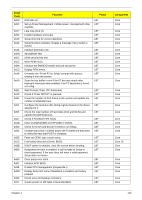

POST Code 0x6B 0x3C 0x3D 0x42 0x46 0x45 0x49 0xC6 0xC5 0x48 0xD1 0xD3 0x24 0xCC 0x8A 0x9D 0x55 0x52 0x54 0x76 0x4A 0x4C 0x59 0x57 0xD6 0x58 0x3F 0xC4 Function If CMOS is bad, load Custom Defaults from flash into CMOS. If successful, reboot. If CMOS is valid, load chipset registers with values from CMOS, otherwise load defaults and display Setup prompt. If Auto Configuration is enabled, always load the chipset registers with the Setup defaults (Rel 6.0). Load alternate registers with CMOS values Initialize interrupt vectors 0 thru 77h Verify the ROM copyright notice Initialize all motherboard devices. 1. Size the PCI bus topology and set bridge bus numbers. 2. Set the system max bus number. 3. Write a 0 to the command register of every PCI device. 4. Write a 0 to all 6 base registers in every PCI device. 5. Write a -1 to the status register of every PC Initialize note dock PnPnd dual CMOS (optional) Verify that the equipment specified in the CMOS matches the hardware currently installed. If the monitor type is set to 00 then a video ROM must exist. If the monitor type is 1 or 2 set the video switch to CGA. If monitor type 3, set the video switch to m Initialize BIOS stack Setup E820h and WAD memory map Set segment-register addressability to 4 GB Redirect Int 10h to enable target board to use a remote serial video (PICO BIOS). Initialize Extended BIOS Data Area and initialize the mouse. Initialize Security Engine. USB Initialization Verify keyboard reset. Initialize keystroke clicker if enabled in Setup. Check status bits for keyboard-related failures. Display error messages on the screen. Initialize all video adapters in system Shadow video BIOS ROM if specified by Setup, and CMOS is valid and the previous boot was OK. Register POST Display Services, fonts, and languages with the POST Dispatch Manager. Initialize 1394 Firewire Initialize PC card Test for unexpected interrupts. First do an STI for hot interrupts. Secondly, test the NMI for an unexpected interrupt. Thirdly, enable the parity checkers and read from memory, checking for an unexpected interrupt. ROMPolit memory init Install the IRQ vectors (Sever Hotkey) Phase LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT 140 Component Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Chapter 4