Acer Aspire 6530G Aspire 6530/6530G Quick Guide - Page 146

POST Code, Function, Phase, Component, define MEM_ERR_CAS_LATENCY S12, S13

|

View all Acer Aspire 6530G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 146 highlights

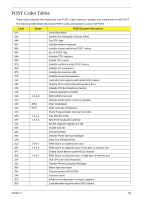

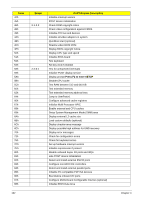

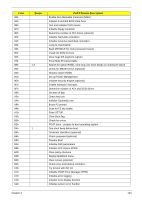

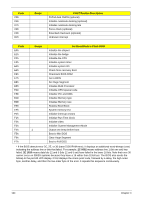

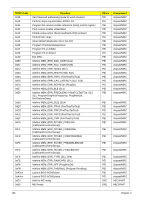

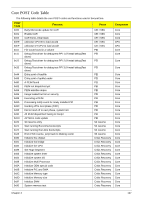

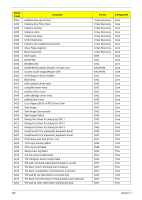

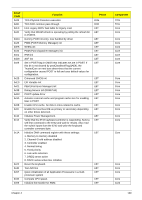

POST Code 0x39 0x40 0x41 0x42 0x43 0x44 0x45 0x46 0x47 0x48 0xAF 0xE0 0xE1 0xE2 0xE3 0xE4 0xE5 0xE6 0xE7 0xE9 0xEA 0xEC 0xED 0xEE 0xEF 0xF0 0xF1 0xF2 0xF6 0xF3 0xF4 0xF5 0xFA 0xFB 0xA0xx 0xA4xx 0xE5 0xE6 Function Set Enhanced addressing mode for each channel Perform steps required after JEDEC init Program the receive enable reference timing control register Post receive enable initialization Enable sense amps. Reset read/write DQS pointers Perform ME steps Clear DRAM initialization bit in the ICH. Program Thermal Management Program TS on DIMM Program TS on Board Exit MRC #define MEM_ERR_BAD_DIMM (S11) #define MEM_ERR_ECC_DIMM (S06) #define MEM_ERR_SIDES (S07) #define MEM_ERR_WIDTH (S08, S10) #define MEM_ERR_TRFC (FindTrasTrpTrcd) #define MEM_ERR_CAS_LATENCY (S12, S13) #define MEM_ERR_REFRESH (ProgDrt) #define MEM_ERR_BL8 (S14) #define MEM_ERR_FREQUENCY (findTCLTacTClk, S13, S12, ProgramGraphicsFrequency, ProgMchOdt, GetPlatformData) #define MEM_ERR_SIZE (S14) #define MEM_ERR_TRAS (FindTrasTrpTrcd) #define MEM_ERR_TRP (FindTrasTrpTrcd) #define MEM_ERR_TRCD (FindTrasTrpTrcd) #define MEM_ERR_TWR (FindTrasTrpTrcd) #define MEM_ERR_RCVEN_FINDLOW (CalibrateRcvenForGroup) #define MEM_ERR_RCVEN_FINDEDGE (CalibrateRcvenForGroup) #define MEM_ERR_RCVEN_FINDPREAMBLE (CalibrateRcvenForGroup) #define MEM_ERR_RCVEN_PREAMBLEEDGE (CalibrateRcvenForGroup) #define MEM_ERR_RCVEN_FINDCENTER (CalibrateRcvenForGroup) #define MEM_ERR_TYPE (S11, S04) #define MEM_ERR_RAWCARD (S11) #define MEM_ERR_SFF (ProgWrioDll) #define MEM_ERR_THERMAL (ProgramThrottling) Launch BIOS ACMSclean Launch BIOS ACMScheck Wait for ME ready ME Ready Phase PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI Component chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI PEI DXE DXE chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC chipset/MRC HECI/iAMT HECI/iAMT 136 Chapter 4