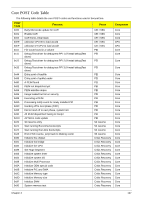

Acer Aspire 6530G Aspire 6530/6530G Quick Guide - Page 149

Function, Phase, Component, PDM Post Dispatcher Manager init - bios update

|

View all Acer Aspire 6530G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 149 highlights

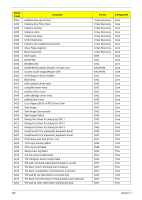

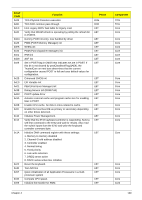

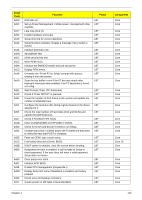

POST Code 0x22 0xB1 0xE3 0x20 0xDA 0x29 0xE5 0x33 0x01 0xD8 0x09 0x2B 0xE0 0xC1 0x3B 0xDC 0x3A 0x0B 0x0F 0x10 0x14 0x1A 0x22 0x40 0x67 0x32 0x69 Function TCG Physical Presence execution TCG DXE common pass through First Legacy BIOS Task table for legacy reset Verify that DRAM refresh is operating by polling the refresh bit in PORTB. Dummy PCIE Init entry, now handled by driver PMM (POST Memory Manager) init WHEA init PDM (Post Dispatcher Manager) init IPMI init ASF Init Set in-POST flag in CMOS that indicates we are in POST. If this bit is not cleared by postClearBootFlagJ(AEh), the TrustedCore on next boot determines that the current configuration caused POST to fail and uses default values for configuration. Enhanced CMOS init EFI Variable Init PEM (Post Error Manager) init Debug Service Init (ROM Polit) POST Update Error Autosize external cache and program cache size for enabling later in POST. Enable CPU cache. Set bits in cmos related to cache. Enable the local bus IDE as primary or secondary depending on other drives detected. Initialize Power Management. Verify that the 8742 keyboard controller is responding. Send a self-test command to the 8742 and wait for results. Also read the switch inputs from the 8742 and write the keyboard controller command byte. Initialize DMA command register with these settings: 1. Memory to memory disabled 2. Channel 0 hold address disabled 3. Controller enabled 4. Normal timing 5. Fixed priority 6. Late write selection 7. DREQ sense active 8. DACK sense active low. Initialize Reset the keyboard. Test A20 line Quick initialization of all Application Processors in a multiprocessor system Compute CPU speed. Initialize the handler for SMM. Phase DXE DXE LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT LBT Chapter 4 Component TCG TCG Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core 139