Hitachi HDS728080PLAT20 Specifications - Page 245

Write Stream DMA 3Ah

|

UPC - 829686000094

View all Hitachi HDS728080PLAT20 manuals

Add to My Manuals

Save this manual to your list of manuals |

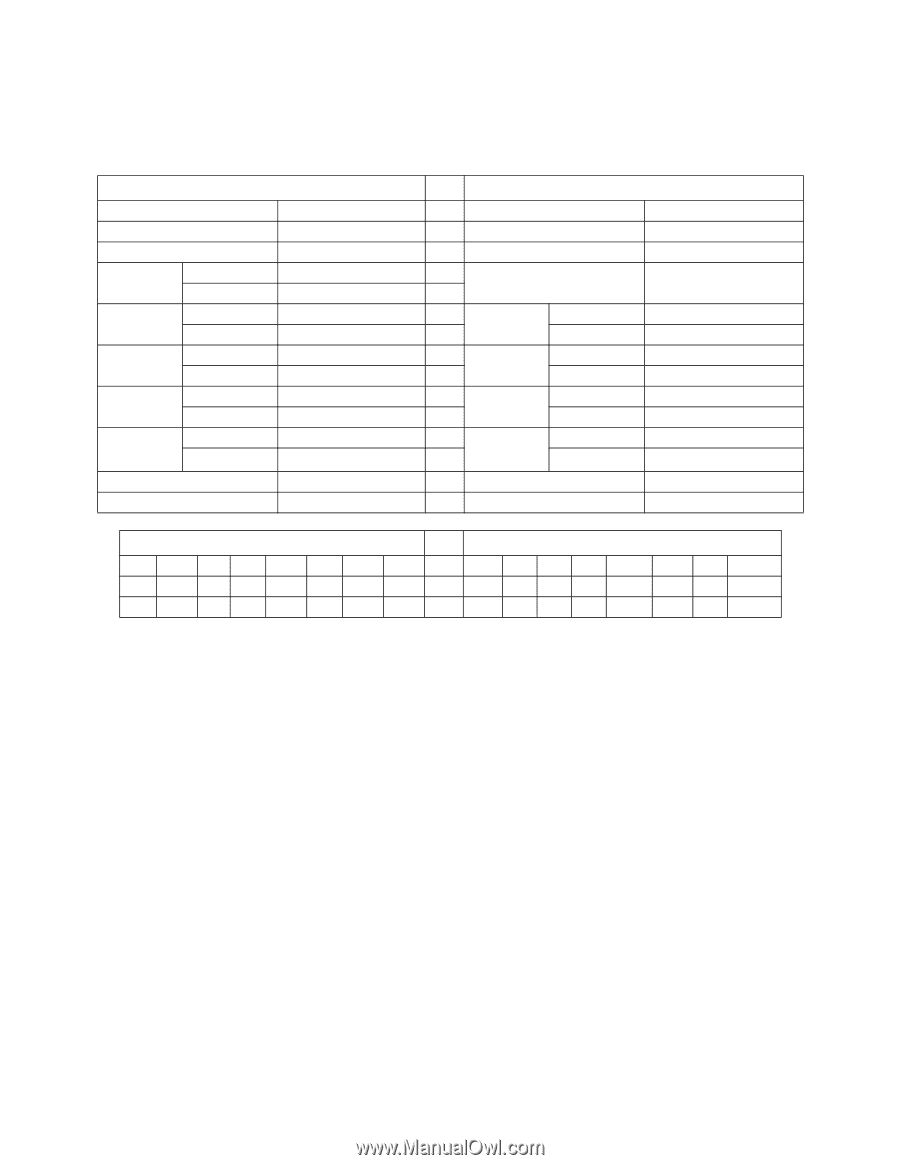

Page 245 highlights

12.54 Write Stream DMA (3Ah) Table 167: Write Stream DMA Command (3Ah) Command Block Output Registers Register 7 6 5 4 3 2 1 0 Data Low Data High Current Feature Previous V V V V - V V V V V V V V V V V Sector Count Current Previous V V V V V V V V V V V V V V V V Sector Number Current Previous V V V V V V V V V V V V V V V V Cylinder Current Low Previous V V V V V V V V V V V V V V V V Cylinder Current V V V V V V V V High Previous V V V V V V V V Device/Head 1 1 1 D - - - - Command 0 0 1 1 1 0 1 0 76 CRC UNC VV Error Register 54 3 2 1 0 0 IDN 0 ABT T0N AMN 0V 0 V 0 V Command Block Input Registers Register 7 6 5 4 3 2 1 0 Data Low Data High Error See below Sector Count HOB=0 HOB=1 Sector Number HOB=0 HOB=1 Cylinder HOB=0 Low HOB=1 Cylinder HOB=0 High HOB=1 Device/Head Status V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V See below ... Status Register 7 654 3 2 1 0 BSY RDY DF DSC DRQ COR IDX ERR 0 VVV - 0 - V The Write Stream DMA command allows the host to write data using the DMA data transfer protocol. This command allows for the host to specify to the device that additional actions need to be performed prior to the completion of the command if the required bits are set. If the Write Continuous bit is set to one, the device shall not stop execution of the command due to errors. If the WC bit is set to one and errors occur in the transfer or writing of the data, the device shall continue to transfer the amount of data requested and then provide ending status with the BSY bit cleared to zero, the SE bit set to one, the ERR bit cleared to zero, and the type of error, ICRC, IDNF, or ABRT, reported in the error log. If the WC bit is set to one and the Command Completion Time Limit expires, the device shall stop execution of the command and provide ending status with BSY bit cleared to zero, the SE bit set to one, the ERR bit cleared to zero, and report the fact that the Command Completion Time Limit expired by setting the CCTO bit in the error log to one, In all cases, the device shall attempt to transfer the amount of data requested within the Command Completion Time Limit event if some data transferred is in error. Deskstar 7K80 Hard Disk Drive Specification 241