Hitachi HDS728080PLAT20 Specifications - Page 46

Ultra DMA timings

|

UPC - 829686000094

View all Hitachi HDS728080PLAT20 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 46 highlights

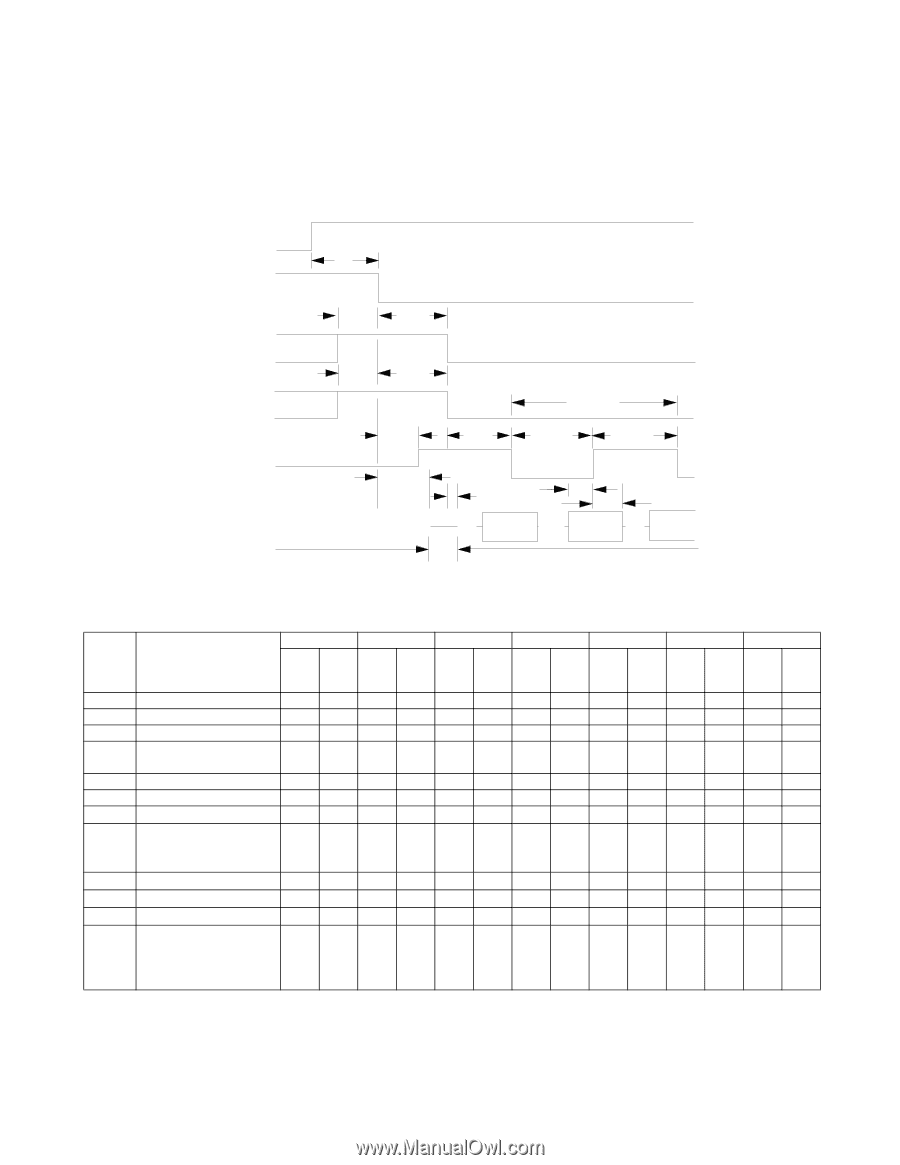

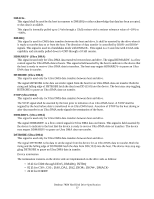

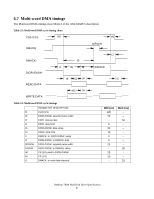

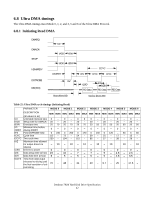

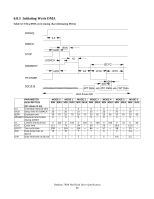

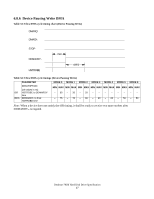

6.8 Ultra DMA timings The Ultra DMA timings meet Mode 0, 1, 2, and 4, 5 and 6 of the Ultra DMA Protocol. 6.8.1 Initiating Read DMA DMARQ DMACKSTOP HDMARDY- tUI tACK tENV tACK tENV tZIORDY DSTROBE tAZ DD(15:0) xxxxxxxxxxxxxxxxxxxxxxxxxxx Host drives DD t2CYC tFS tCYC tCYC tZAD tDS tDH xxx RD Data xxxx RD Data xxx RD Data Device drives DD Table 25: Ultra DMA cycle timings (Initiating Read) PARAMETER MODE 0 MODE 1 MODE 2 MODE 3 MODE 4 MODE 5 MODE 6 DESCRIPTION MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX (all values in ns) tUI Unlimited interlock time 0 - 0 - 0 0 0 - 0 - 0 - 0 - tACK Setup time for DMACK- 20 - 20 - 20 - 20 - 20 - 20 - 20 - tENV Envelope time 20 70 20 70 20 70 20 55 20 55 20 50 20 50 tZI- Minimum time before ORDY driving IORDY 0-0-0-0-0-0-0- tFS First DSTROBE time 0 230 0 200 0 170 0 130 0 120 - 90 0 80 tCYC Cycle time 112 - 73 - 54 - 39 - 25 - 17 - 13 - t2CYC Two cycle time 230 - 154 - 115 - 86 - 57 - 38 - 29 - tAZ Maximum time allowed for output drivers to - 10 - 10 - 10 - 10 - 10 10 - 10 release tZAD Drivers to assert 0-0-0-0-0-0-0- tDS Data setup time at host 15 - 10 - 7 - 7 - 5 - 4.8 - 2.6 - tDH Data hold time at host 5 - 5 - 5 - 5 - 5 - 4.8 - 3.5 - tDZFS Time from data ouput released-to-driving until the first transition of crit- 70 - 48 - 31 - 20 - 6.7 - 25 - 17.5 - ical timing Deskstar 7K80 Hard Disk Drive Specification 42