IBM DTCA-24090 Hard Drive Specifications - Page 52

Ultra DMA Timings

|

View all IBM DTCA-24090 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

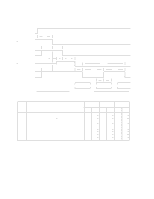

6.5.3 Ultra DMA Timings The Ultra DMA timing meets Mode 0, 1 and 2 of the Ultra DMA/33 -- a Proposal for a New Protocol in ATA/ATAPI-4 (X3T13/D96153 Revision 1) 6.5.3.1 Initiating Read DMA DMARQ DMACK STOP HDMARDY DSTROBE DB(15:00) < Tui > Tzrdy > < < < Tfs > < T2cyc > Tcyc > < Tcyc > Taz < > XXXXXXXXXXXXXXX > Host drives DB < > Tzad > Tdvs Tdvh < XXX RD Data XXX RD Data XXX RD Data < Device drives DB PARAMETER DESCRIPTION Tui Tack Tenv Tzrdy Tfs Tcyc T2cyc Taz Tzad Tdvs Tdvh Unlimited interlock time Setup time before DMACK assertion Envelope time Wait time before driving DSTROBE First strobe time Cycle Time 2 Cycle time Output release time Output enable time Data setup time (at device side) Data Hold time (at device side) Figure 27. Ultra D M A cycle timings (Initiating Read) [nsec] MODE0 MODE1 MODE2 MIN MAX MIN MAX MIN MAX 0 0 0 20 20 20 20 70 20 70 20 70 0 0 0 0 230 0 200 0 170 114 75 55 235 156 117 10 10 10 0 0 0 70 48 34 6 6 6 44 OEM Specifications of DTCA-2xxxx 2.5 inch H D D