HP Model 712/100 hp 9000 series 700 model 712 service handbook (a2615-90039) - Page 64

HPMC Caused by a Multi-Bit Memory Parity Error

|

View all HP Model 712/100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 64 highlights

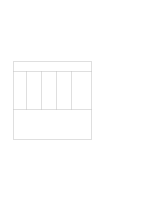

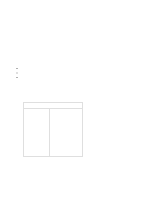

Table 4-1. PIM Action Table Check Type Cache Check Bus Check Word Word Word System Responder Word Action * See Note 1 0x80000000 0x40000000 N/A N/A Replace Motherboard 0x20000000 N/A 0X00210000 0X00000000 Replace SIMM 0xEFFFFFFF See Note 2 0x20000000 N/A 0x00310000 0xF0000000 Replace 0xF01FFFFF Motherboard 0x20000000 N/A 0x00310000 0xF0200000 Replace Optional 0xFFBFFFFF I/O Card 0x20000000 N/A 0x00310000 0xFFFBF000 Replace 0xFFFFFFFF Motherboard Note 1 When more than one failed FRU is identified, run the appropriate diagnostics to isolate the failed FRU. Note 2 While Architected Main Memory space is from 0x00000000 through 0xEFFFFFFF, the Model 712 can only use up to 128 MB (192 MB for the 712/100). With this limitation any memory address from 0x10000000 (0X14000000 for the 712/100) through 0xEFFFFFFF is invalid, and, if given in the System Responder word, the Motherboard should (usually) be replaced. If the error occurs again, there is a probable Kernel problem. See HPMC Caused by a Multi-Bit Memory Parity Error for information on identifying the failed SIMM. HPMC Caused by a Multi-Bit Memory Parity Error An HPMC interruption is forced when a multi-bit memory parity error is detected during a "DMA read" operation of fetching an I/D cache line (32 bytes). Examine the 12 words listed under Other Processor Data of the data returned from a pim command during the Boot Administration environment. These words represent the following data: Other Processor Data IIA Space IIA Offset Reserved Cache Check Assists Check Reserved Check Type TLB Check Assist State CPU State Bus Check System Responder Address Table 4-2 shows an example of the values for these words: Troubleshooting 4-5