HP Model 712/100 hp 9000 series 700 model 712 service handbook (a2615-90039) - Page 68

HPMC Caused by a Data Cache Parity Error

|

View all HP Model 712/100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 68 highlights

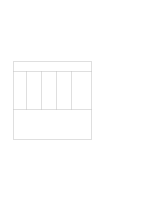

HPMC Caused by a Data Cache Parity Error An HPMC interruption is forced when a data parity error is detected during a Load instruction to the memory address space or during a data cache flush operation. Examine the 12 words listed under Other Processor Data of the data returned from a pim command during the Boot Administration environment. These words represent the following data: Other Processor Data IIA Space IIA Offset Reserved Cache Check Assists Check Reserved Check Type TLB Check Assist State CPU State Bus Check System Responder Address Table 4-4 shows an example of the values for these words: Table 4-4. Processor Module Error (Data Cache Parity) Word Check Type CPU State Cache Check TLB Check Bus Check Assists Check Assists State System Responder Address Value 0x80000000 0x9e000004 0x40000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 The value in the CPU State word indicates that register values and addresses stored in Stable Storage at the time of the HPMC were saved. The value on the Cache Check word identifies that logic in the processor module detected a (data) cache parity error. Replace the Motherboard. Troubleshooting 4-9