Intel BX80605X3430 Data Sheet - Page 38

Thread and Core C-State Entry and Exit, Table 4-3., Coordination of Thread Power States

|

UPC - 735858210331

View all Intel BX80605X3430 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 38 highlights

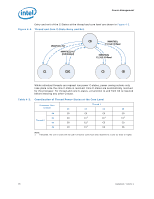

Power Management Entry and exit of the C-States at the thread and core level are shown in Figure 4-2. Figure 4-2. Thread and Core C-State Entry and Exit MWAIT(C1), HLT MWAIT(C1), HLT (C1E Enabled) C0 MWAIT(C6), P_LVL3 I/O Read MWAIT(C3), P_LVL2 I/O Read C1 C1E C3 C6 While individual threads can request low power C-states, power saving actions only take place once the core C-state is resolved. Core C-states are automatically resolved by the processor. For thread and core C-states, a transition to and from C0 is required before entering any other C-state. Table 4-3. Coordination of Thread Power States at the Core Level Processor Core Thread 1 C-State C0 C1 C3 C6 C0 C0 C0 C0 C0 C1 C0 Thread 0 C3 C0 C11 C11 C11 C3 C11 C3 C6 C0 C11 C3 C6 Note: 1. If enabled, the core C-state will be C1E if all active cores have also resolved to a core C1 state or higher. 38 Datasheet, Volume 1