Intel BX80605X3430 Data Sheet - Page 68

Table 7-3., Signal Groups Sheet 2 of 2

|

UPC - 735858210331

View all Intel BX80605X3430 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 68 highlights

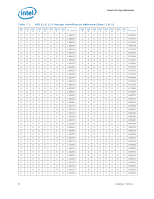

Electrical Specifications Table 7-3. Signal Groups (Sheet 2 of 2)1 Signal Group Single Ended Single Ended Alpha Group (qb) (r) Single Ended (s) Single Ended Single Ended Power/Ground/Other Single Ended PCI Express* Differential Differential Single Ended DMI Differential Differential Intel® FDI Single Ended Differential (t) (ta) (u) (v) (w) (x) (y) (z) (ac) (ad) (ae) (af) (ag) (ah) (ai) Type CMOS Input CMOS Output CMOS Bi-directional Analog Input Analog Output Signals RSTIN# VTT_SELECT VID[7:6] VID[5:3]/CSC[2:0] VID[2:0]/MSID[2:0] COMP0, COMP1, COMP2, COMP3, SM_RCOMP[2:0], ISENSE SA_DIMM_VREFDQ SB_DIMM_VREFDQ Power Ground No Connect Asynchronous CMOS Output Sense Points Other VCC, VCC_NCTF, VTT, VCCPLL, VDDQ, VAXG VSS, CGC_TP_NCTF RSVD, RSVD_NCTF, RSVD_TP, FC_x PSI# VCC_SENSE, VSS_SENSE, VTT_SENSE, VSS_SENSE_VTT, VAXG_SENSE, VSSAXG_SENSE SKTOCC#, DBR# PCI Express Input PCI Express Output Analog Input PEG_RX[15:0], PEG_RX#[15:0] PEG_TX[15:0], PEG_TX#[15:0] PEG_ICOMP0, PEG_ICOMPI, PEG_RCOMP0, PEG_RBIAS DMI Input DMI Output FDI Input FDI Output DMI_RX[3:0], DMI_RX#[3:0] DMI_TX[3:0], DMI_TX#[3:0] FDI_FSYNC[1:0]4, FDI_LSYNC[1:0]4, FDI_INT4 FDI_TX[7:0]4, FDI_TX#[7:0]4 Notes: 1. Refer to Chapter 6 for signal description details. 2. SA and SB refer to DDR3 Channel A and DDR3 Channel B. 3. These signals are only used on processors and platforms that support ECC DIMMs. 4. These signals will not be actively used on the Intel Xeon processor 3400 series. All Control Sideband Asynchronous signals are required to be asserted/de-asserted for at least eight BCLKs for the processor to recognize the proper signal state. See Section 7.9 for the DC specifications. 68 Datasheet, Volume 1