Intel BX80605X3430 Data Sheet - Page 81

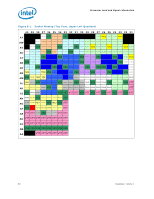

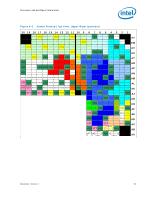

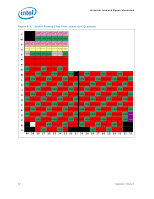

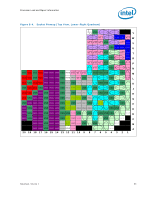

Socket Pinmap Top View, Upper-Right Quadrant

|

UPC - 735858210331

View all Intel BX80605X3430 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 81 highlights

Processor Land and Signal Information Figure 8-2. Socket Pinmap (Top View, Upper-Right Quadrant) 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 VDDQ VDDQ VDDQ VSS VSS SB_MA[4] SB_MA[9] SA_MA[1] SA_MA[5] SB_MA[14] SA_CKE[3] SB_CKE[1] SA_DQ[27] SA_DQS[3] SA_DQ[25] RSVD_NCTF 1 AY VDDQ SA_MA[0] SB_MA[6] SB_MA[11] SB_MA[12] SA_MA[4] SA_MA[7] SA_MA[9] SA_MA[12] SA_CKE[1] SB_CKE[0] SA_DQ[31] SA_DQS#[3] SA_DQ[24] SA_DQ[19] SA_DQ[18] RSVD_NCTF AW VDDQ VDDQ VDDQ VSS SA_BS[0] SB_MA[2] SB_MA[5] SA_MA[2] SA_MA[6] SB_BS[2] SB_MA[15] SA_CKE[2] SB_CKE[3] SM_DRAMRST# SA_DQ[30] SA_DM[3] SA_DQ[29] SA_DQ[23] SA_DQ[22] RSVD_NCTF AV SB_MA[0] SA_BS[1] SB_MA[1] SB_MA[3] SB_MA[7] SA_MA[3] VDDQ VSS VSS SA_MA[8] SA_MA[11] SA_BS[2] SA_CKE[0] SB_CKE[2] SA_DQ[26] SA_DQ[28] SA_DQS[2] SA_DQS#[2] SA_DQ[17] SA_DM[2] AU VSS VSS VSS VSS VSS VSS VDDQ SA_RAS# SA_MA[10] SB_MA[8] SB_CK[1] SB_ECC_CB[1] VDDQ SA_MA[14] SB_DQ[31] SB_DM[3] SB_DQ[24] SA_DQ[16] SA_DQ[20] SA_DQ[21] AT VSS SB_CK[3] SB_CK#[3] SB_CK[0] SB_CK#[0] SB_CK#[1] SB_DQS[8] SB_DQS#[8] SB_ECC_CB[0] SA_ECC_CB[2] SA_MA[15] SB_DQ[26] SB_DQS[3] SB_DQ[25] SB_DQ[29] SB_DQ[19] SA_DQ[15] SA_DQ[10] SA_DQ[11] VSS AR VSS VSS VSS VSS VSS VSS VSS VSS SA_CK[3] SA_CK[1] SB_ECC_CB[3] SB_ECC_CB[7] SA_ECC_CB[3] SA_ECC_CB[0] SB_DQS#[3] SB_DQ[18] SB_DQ[23] SA_DQS#[1] SA_DQS[1] SA_DQ[14] AP VSS VSS VSS VSS SA_CK#[3] SA_CK#[1] SB_CK[2] SB_CK#[2] SB_ECC_CB[2] SB_ECC_CB[6] SB_ECC_CB[5] RSVD_TP SA_ECC_CB[1] SB_DQ[28] SB_DQ[22] SB_DQS[2] SB_DQ[17] SA_DQ[8] SA_DQ[9] SA_DM[1] AN RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD VSS VSS VSS AM SB_ECC_CB[4] SA_ECC_CB[7] SA_DQS#[8] SB_DQ[27] SB_DM[2] SB_DQS#[2] SB_DQ[21] SA_DQ[12] SA_DQ[13] VTT VSS VSS VSS VSS VSS VSS AL RSVD RSVD RSVD RSVD RSVD SA_DQS[8] SA_ECC_CB[5] SB_DQ[30] SB_DQ[16] SB_DQ[20] SB_DQ[11] SA_DQ[2] SA_DQ[3] VTT VTT VSS VSS VSS VSS VSS AK RSVD RSVD RSVD RSVD RSVD RSVD SA_ECC_CB[6] SA_ECC_CB[4] SB_DQ[15] SB_DQ[10] SA_DQS[0] SA_DQ[7] SA_DQ[6] VSS VTT VSS VTT VSS VDDQ VSS VDDQ VSS VDDQ VSS VSS VSS SB_DQ[3] SB_DQ[14] SB_DQS#[1] SA_DQ[1] SA_DQS#[0] SA_DM[0] AJ VSS VSS SB_DQ[2] SB_DQ[9] SB_DQS[1] SB_DM[1] SA_DQ[5] SA_DQ[0] AH VSS VCCPLL SB_DQ[12] SB_DQ[8] SB_DQ[13] SB_DIMM_VREFDQ SA_DQ[4] SM_RCOMP[0] AG VSS VSS VCCPLL VCCPLL COMP1 SB_DQ[6] SB_DQS[0] SA_DIMM_VREFDQ AF VTT VSS VSS AE SB_DQ[7] SB_DQS#[0] SB_DM[0] RSVD SM_RCOMP[2] VSS VSS SB_DQ[0] SB_DQ[1] FDI_LSYNC[0] FDI_LSYNC[1] RSVD SM_RCOMP[1] AD VTT VTT VSS SB_DQ[4] SB_DQ[5] FDI_INT FDI_FSYNC[0] FDI_FSYNC[1] AC VSS VTT VSS VSS PM_EXT_TS#[0] PM_EXT_TS#[1] AB VSS BCLK[1] BCLK[0] BCLK#[0] PEG_CLK# PEG_CLK AA Datasheet, Volume 1 81