Intel BX80605X3430 Data Sheet - Page 56

Error and Thermal Protection

|

UPC - 735858210331

View all Intel BX80605X3430 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 56 highlights

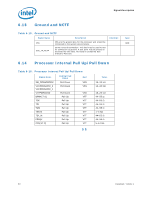

Signal Description 6.9 Error and Thermal Protection Table 6-11. Error and Thermal Protection Signal Name CATERR# PECI PROCHOT# PSI# THERMTRIP# Description Catastrophic Error: This signal indicates that the system has experienced a catastrophic error and cannot continue to operate. The processor will set this for non-recoverable machine check errors or other unrecoverable internal errors. Since this is an I/O pin, external agents are allowed to assert this pin that will cause the processor to take a machine check exception. CATERR# is used for signaling the following types of errors: • Legacy MCERR: CATERR# is asserted for 16 BCLKs. • Legacy IERR: CATERR# remains asserted until warm or cold reset. PECI (Platform Environment Control Interface) is the serial sideband interface to the processor and is used primarily for thermal, power, and error management. PROCHOT# goes active when the processor temperature monitoring sensor(s) detects that the processor has reached its maximum safe operating temperature. This indicates that the processor Thermal Control Circuit has been activated, if enabled. This signal can also be driven to the processor to activate the Thermal Control Circuit. This signal does not have on-die termination and must be terminated on the system board. Processor Power Status Indicator: This signal is asserted when maximum possible processor core current consumption is less than 15 A. Assertion of this signal is an indication that the VR controller does not currently need to be able to provide ICC above 15 A, and the VR controller can use this information to move to more efficient operating point. This signal will de-assert at least 3.3 s before the current consumption will exceed 15 A. The minimum PSI# assertion and de-assertion time is 1 BCLK. Thermal Trip: The processor protects itself from catastrophic overheating by use of an internal thermal sensor. This sensor is set well above the normal operating temperature to ensure that there are no false trips. The processor will stop all execution when the junction temperature exceeds approximately 125 °C. This is signaled to the system by the THERMTRIP# pin. Direction I/O I/O I/O O O Type GTL Asynch Asynch GTL Asynch CMOS Asynch GTL 56 Datasheet, Volume 1