Intel E3300 Data Sheet - Page 24

Processor DC Specifications

|

View all Intel E3300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

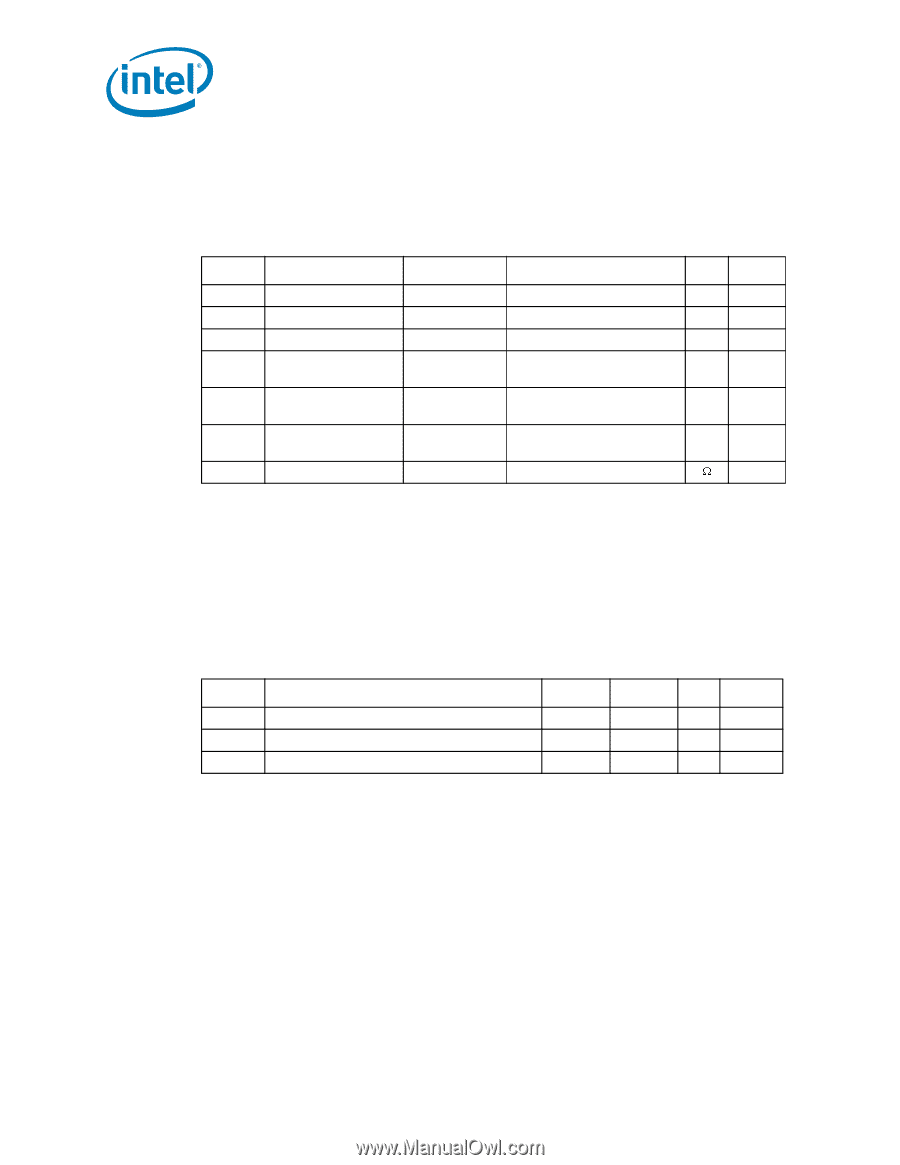

Electrical Specifications 2.7.3 Table 10. Table 11. Processor DC Specifications The processor DC specifications in this section are defined at the processor core (pads) unless otherwise stated. All specifications apply to all frequencies and cache sizes unless otherwise stated. GTL+ Signal Group DC Specifications Symbol Parameter Min Max Unit Notes1 VIL Input Low Voltage -0.10 GTLREF - 0.10 V 2, 5 VIH Input High Voltage GTLREF + 0.10 VTT + 0.10 V 3, 4, 5 VOH Output High Voltage VTT - 0.10 VTT V 4, 5 IOL Output Low Current N/A VTT_MAX / [(RTT_MIN) + (2 * RON_MIN)] A - ILI Input Leakage Current N/A ± 100 µA 6 ILO Output Leakage Current N/A ± 100 µA 7 RON Buffer On Resistance 7.49 9.16 NOTES: 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies. 2. VIL is defined as the voltage range at a receiving agent that will be interpreted as a logical low value. 3. VIH is defined as the voltage range at a receiving agent that will be interpreted as a logical high value. 4. VIH and VOH may experience excursions above VTT. 5. The VTT referred to in these specifications is the instantaneous VTT. 6. Leakage to VSS with land held at VTT. 7. Leakage to VTT with land held at 300 mV. Open Drain and TAP Output Signal Group DC Specifications Symbol Parameter Min Max Unit Notes1 VOL Output Low Voltage IOL Output Low Current ILO Output Leakage Current 0 0.20 V - 16 50 mA 2 N/A ± 200 µA 3 NOTES: 1. Unless otherwise noted, all specifications in this table apply to all processor frequencies. 2. Measured at VTT * 0.2 V. 3. For Vin between 0 and VOH. 24 Datasheet