SanDisk SDCFH-004G Product Manual - Page 36

Register Transfer to/from Device, Table 3-15

|

UPC - 878587001044

View all SanDisk SDCFH-004G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 36 highlights

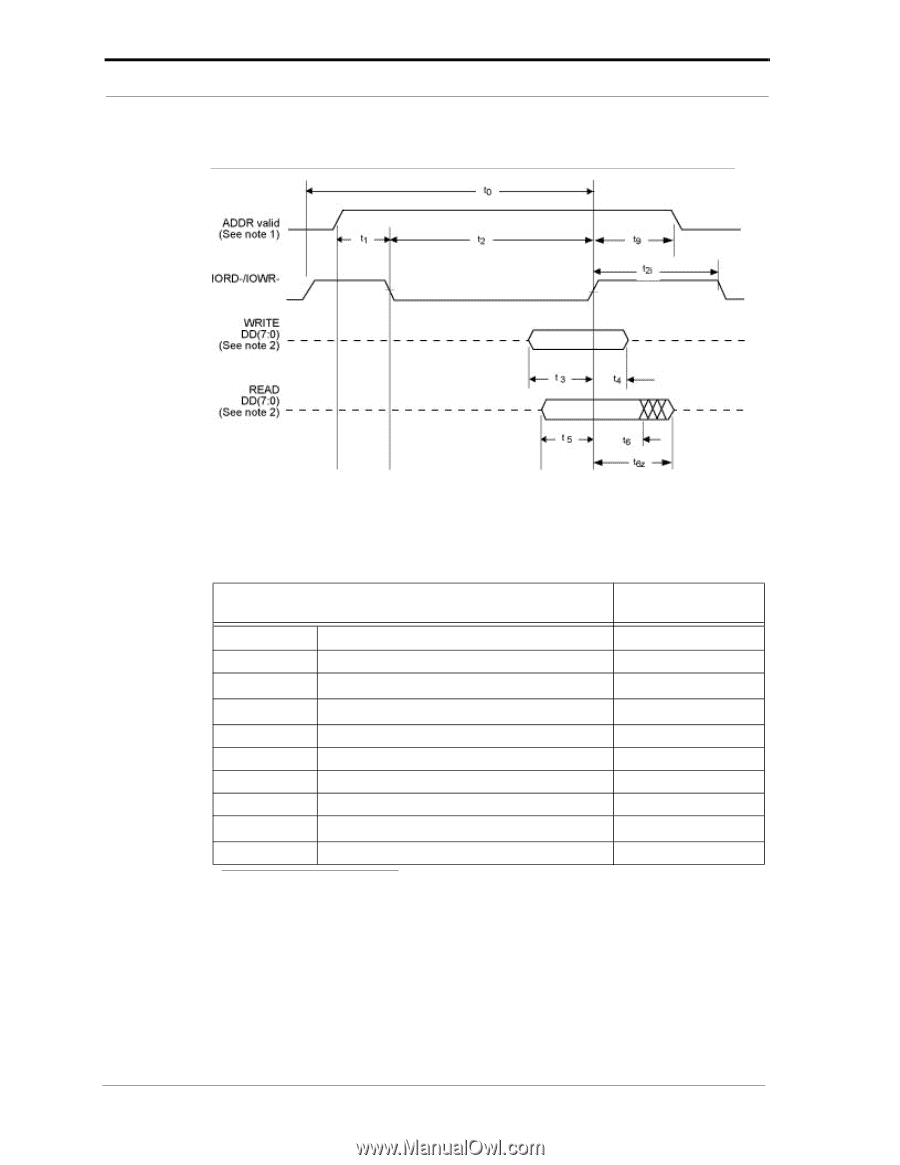

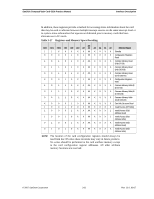

Interface Description SanDisk CompactFlash Card OEM Product Manual Figure 3-7 Register Transfer to/from Device NOTE 1: NOTE 2: Device address consists of signals -CS0, -CS1 and -DA(2:0). Data consists of DD(7:0). Table 3-15 Register Transfer to/from Device PIO Timing Parameters t0 a Cycle time (min.) t1 Address valid to IORD-/IOWR- setup (min.) t2 a IORD-/IOWR- pulse width 8-bit (min.) t2i a IORD-/IOWR- recovery time (min.) t3 IOWR- data setup (min.) t4 IOWR- data hold (min.) t5 IORD- data setup (min.) t6 IORD- data hold (min.) t6z b IORD- data tri-state (max.) t9 IORD-/IOWR- to address valid hold (min.) Mode 4 (ns) 120 25 70 25 20 10 20 5 30 10 a. t0 is the minimum total cycle time, t2 is the minimum command active time, and t2i is the minimum command recovery time or command inactive time. The actual cycle time equals the sum of the actual command active time and the actual command inactive time. The three timing requirements of t0, t2, and t2i shall be met. The minimum total cycle time requirements are greater than the sum of t2 and t2i. This means a host implementation may lengthen either or both t2 or t2i to ensure that t0 is equal to or greater than the value reported in the devices IDENTIFY DEVICE data. A device imple mentation shall support any legal host implementation. b. This parameter specifies the time from the negation edge of /IORD to the time that the data bus is no longer driven by the device (tri-state). 02/07, Rev. 12.0 3-18 © 2007 SanDisk Corporation