SanDisk SDCFH-004G Product Manual - Page 55

ATA Command Description

|

UPC - 878587001044

View all SanDisk SDCFH-004G manuals

Add to My Manuals

Save this manual to your list of manuals |

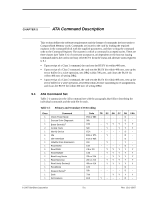

Page 55 highlights

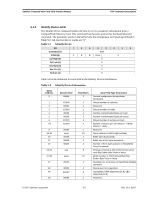

CHAPTER 5 ATA Command Description This section defines the software requirements and the format of commands the host sends to CompactFlash Memory cards. Commands are issued to the card by loading the required registers in the command block with the supplied parameters, and then writing the command code to the Command Register. The manner in which a command is accepted varies. There are three classes (see Table 5-1) of command acceptance, all dependent on the host not issuing commands unless the card is not busy. (The BUSY bit in the status and alternate status registers is 0.) • Upon receipt of a Class 1 command, the card sets the BUSY bit within 400 nsec. • Upon receipt of a Class 2 command, the card sets the BUSY bit within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 700 µsec, and clears the BUSY bit within 400 nsec of setting DRQ. • Upon receipt of a Class 3 command, the card sets the BUSY bit within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 20 msec (assuming no re-assignments), and clears the BUSY bit within 400 nsec of setting DRQ. 5.1 ATA Command Set Table 5-1 summarizes the ATA command set with the paragraphs that follow describing the individual commands and the task file for each. Table 5-1 Primary and Secondary I/O Decoding Class 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Command Check Power Mode Execute Drive Diagnostic Erase Sector(s)a Format Track Identify Device Idle Idle Immediate Initialize Drive Parameters Read Buffer Read DMA Read Multiple Read Long Sector Read Sector(s) Read Verify Sector(s) Recalibrate Request Senseb Seek Set Features Code FR SC SN CY DH LBA E5h or 98h - - - - D - 90h - - - - D - C0h - YYYY Y 50h -Y - YY Y ECh - - - - D - E3h or 97h - Y - - D - E1h or 95h - - - - D - 91h -Y - - Y - E4h - - - - D - C8 or C9 - YYYY Y C4h - YYYY Y 22h or 23h - - YY Y Y 20h or 21h - Y Y Y Y Y 40h or 41h - Y Y Y Y Y 1Xh - - - - D - 03h - - - - D - 7Xh - - YY Y Y EFh Y - - - D - © 2007 SanDisk Corporation 5-1 Rev. 12.0, 02/07