Fujitsu MPD3173AT Product Manual - Page 39

Cable configuration

|

View all Fujitsu MPD3173AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

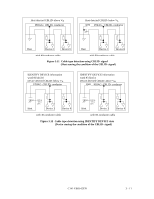

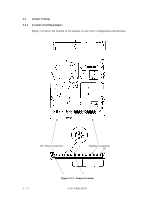

Pin 40 (Ground) Pin 34 Pin 30 (Ground) Pin 26 (Ground) Pin 24 (Ground) Pin 22 (Ground) Pin 19 (Ground) Pin 2 (Ground) 254.0 to 457.2 mm (10 to 18 inch) 127.0 to 304.8 mm 101.6 to 152.4 mm (5 to 12 inch) (4 to 6 inch) open Symbolizes Pin 34 Conductor being cut Position 1 Pin 34 contact (PDIAG-:CBLID- signal) System Board Connector Connector 1 Figure 3.10 Cable configuration Connector 2 b) Host system that do not support Ultra DMA modes greater than mode 2 shall not connect to the PDIAG-:CBLID- signal. c) Host system that do support Ultra DMA modes greater than mode 2 shall either connect directly to the device without using a cable assembly, or determine the cable assembly type. Determining the cable assembly type may be done either by the host sensing the condition of the PDIAG-:CBLID- signal (see Figure 3.11), or by relying on information from the device (see Figure 3.12). Hosts that rely on information from the device shall have a 0.047 µF capacitor connected from the PDIAG-:CBLID- signal to ground. The tolerance on this capacitor shall be 20% or less. 3 - 10 C141-E069-02EN