Fujitsu MPD3173AT Product Manual - Page 74

Table 5.3, I/O registers, Notes

|

View all Fujitsu MPD3173AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 74 highlights

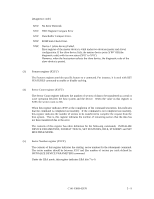

Table 5.3 I/O registers CS0- CS1- DA2 DA1 I/O registers DA0 Read operation Write operation Command block registers 1 0 0 0 0 Data Data 1 0 0 0 1 Error Register Features 1 0 0 1 0 Sector Count Sector Count 1 0 0 1 1 Sector Number Sector Number 1 0 1 0 0 Cylinder Low Cylinder Low 1 0 1 0 1 Cylinder High Cylinder High 1 0 1 1 0 Device/Head Device/Head 1 0 1 1 1 Status Command 1 1 X X X (Invalid) (Invalid) Control block registers 0 1 1 1 0 Alternate Status Device Control 0 1 1 1 1 - - Host I/O address X'1F0' X'1F1' X'1F2' X'1F3' X'1F4' X'1F5' X'1F6' X'1F7' - X'3F6' X'3F7' Notes: 1. The Data register for read or write operation can be accessed by 16 bit data bus (DATA0 to DATA15). 2. The registers for read or write operation other than the Data registers can be accessed by 8 bit data bus (DATA0 to DATA7). 3. When reading the Drive Address register, bit 7 is high-impedance state. 4. The LBA mode is specified, the Device/Head, Cylinder High, Cylinder Low, and Sector Number registers indicate LBA bits 27 to 24, 23 to 16, 15 to 8, and 7 to 0. C141-E069-02EN 5 - 7