Fujitsu MPD3173AT Product Manual - Page 79

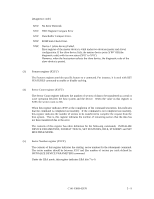

Command register X'1F7

|

View all Fujitsu MPD3173AT manuals

Add to My Manuals

Save this manual to your list of manuals |

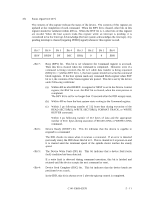

Page 79 highlights

- Bit 3: - Bit 2: - Bit 1: - Bit 0: Data Request (DRQ) bit. This bit indicates that the device is ready to transfer data of word unit or byte unit between the host system and the device. Always 0. Always 0. Error (ERR) bit. This bit indicates that an error was detected while the previous command was being executed. The Error register indicates the additional information of the cause for the error. (10) Command register (X'1F7') The Command register contains a command code being sent to the device. After this register is written, the command execution starts immediately. Table 5.3 lists the executable commands and their command codes. This table also lists the necessary parameters for each command which are written to certain registers before the Command register is written. 5 - 12 C141-E069-02EN