HP ProLiant DL185 HP ProLiant DL185 Generation 5 Server Software Configuration - Page 34

Beep codes and checkpoint codes, Shadow system BIOS ROM

|

View all HP ProLiant DL185 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

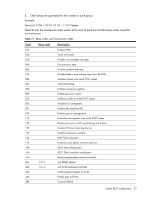

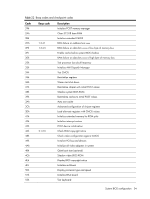

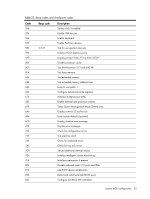

Table 22 Beep codes and checkpoint codes Code 29h 2Ah 2Bh 2Ch 2Eh 2Fh 30h 32h 33h 34h 35h 36h 37h 38h 39h 3Ah 3Ch 3Dh 41h 42h 45h 46h 48h 49h 4Ah 4Bh 4Ch 4Eh 4Fh 50h 51h 52h Beep code 1-3-4-1 1-3-4-3 2-1-2-3 Description Initialize POST memory manager Clear 512 KB base RAM Initialize extended CMOS RAM failure on address line xxxx RAM failure on data bits xxxx of low byte of memory bus Enable cache before system BIOS shadow RAM failure on data bits xxxx of high byte of memory bus Test processor bus-clock frequency Initialize AMI Dispatch Manager Test CMOS Reinitialize registers Warm start shut down Reinitialize chipset with initial POST values Shadow system BIOS ROM Reinitialize caches to initial POST values Auto size cache Advanced configuration of chipset registers Load alternate registers with CMOS values Initialize extended memory for ROM pilot Initialize interrupt vectors POST device initialization Check ROM copyright notice Check video configuration against CMOS Initialize PCI bus and devices Initialize all video adapters in system Quiet boot start (optional) Shadow video BIOS ROM Display BIOS copyright notice Initialize multi-boot Display processor type and speed Initialize EISA board Test keyboard System BIOS configuration 34