Nintendo DMG-01 Manual - Page 138

V 1.01

|

View all Nintendo DMG-01 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 138 highlights

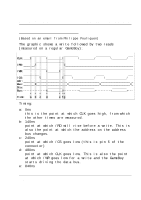

5.2. Typical timing diagram Game BoyTM CPU Manual point at which /WR goes high after a write. f: 960ns point at which CLK goes high. This is also the point at which /CS goes high and the GameBoy stops driving the data bus. g: 990ns point at which /RD goes low for a read (30ns after CLK goes high). (Measurements roundet to the nearest 10ns) "Some devices (like disk controller chips) require that the address be valid before you access them (with a read or write pulse). The problem is that /RD doesn't go high between consecutive reads, and the second problem is that when /RD transitions, it does so at the same time (or before) the address changes. The result is that from the device's perspective, an address transition looks like a bunch of reads from random addresses. These spurious reads are ok for RAM and ROM, but can really screw things up for devices with internal buffers, because they may be fooled into thinking that you have read more data from them than you actually have. The way to solve this problem is to feed CLK and /RD through a OR gate. The downside is that it makes your allowable read time shorter. Page 138 V 1.01