Nintendo DMG-01 Manual - Page 34

Interrupt Descriptions

|

View all Nintendo DMG-01 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

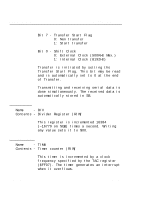

2.12.2. Interrupt Descriptions Game BoyTM CPU Manual 2.12.2. Interrupt Descriptions The following interrupts only occur if they have been enabled in the Interrupt Enable register ($FFFF) and if the interrupts have actually been enabled using the EI instruction. 1. V-Blank The V-Blank interrupt occurs ~59.7 times a second on a regular GB and ~61.1 times a second on a Super GB (SGB). This interrupt occurs at the beginning of the V-Blank period. During this period video hardware is not using video ram so it may be freely accessed. This period lasts approximately 1.1 ms. 2. LCDC Status There are various reasons for this interrupt to occur as described by the STAT register ($FF40). One very popular reason is to indicate to the user when the video hardware is about to redraw a given LCD line. This can be useful for dynamically controlling the SCX/SCY registers ($FF43/$FF42) to perform special video effects. 3. Timer Overflow This interrupt occurs when the TIMA register ($FF05) changes from $FF to $00. 4. Serial Transfer Completion This interrupt occurs when a serial transfer has completed on the game link port. Page 34 V 1.01