Nintendo DMG-01 Manual - Page 7

Game Boy, CPU Manual, by DP

|

View all Nintendo DMG-01 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

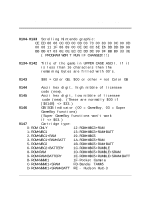

Game BoyTM CPU Manual 2.4. Processor have been added and some have been taken away. The following are added instructions: ADD SP,nn LDI (HL),A LDD (HL),A LDI A,(HL) LDD A,(HL) LD A,($FF00+nn) LD A,($FF00+C) LD ($FF00+nn),A LD ($FF00+C),A LD (nnnn),SP LD HL,SP+nn STOP SWAP r ;nn = signed byte ;Write A to (HL) and increment HL ;Write A to (HL) and decrement HL ;Write (HL) to A and increment HL ;Write (HL) to A and decrement HL ;nn = signed byte ;Stop processor & screen until button press ;Swap high & low nibbles of r The following instructions have been removed: Any command that uses the IX or IY registers. All IN/OUT instructions. All exchange instructions. All commands prefixed by ED (except remapped RETI). All conditional jumps/calls/rets on parity/overflow and sign flag. The following instructions have different opcodes: LD A,[nnnn] LD [nnnn],A RETI by DP Page 7