Nintendo DMG-01 Manual - Page 39

FF06 TMA, FF07 TAC, FF0F IF

|

View all Nintendo DMG-01 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

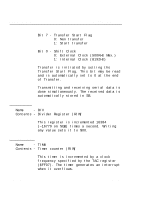

Game BoyTM CPU Manual 2.13.1. I/O Registers 6. FF06 (TMA) Name - TMA Contents - Timer Modulo (R/W) When the TIMA overflows, this data will be loaded. 7. FF07 (TAC) Name - TAC Contents - Timer Control (R/W) Bit 2 - Timer Stop 0: Stop Timer 1: Start Timer Bits 1+0 - Input Clock Select 00: 4.096 KHz (~4.194 KHz SGB) 01: 262.144 Khz (~268.4 KHz SGB) 10: 65.536 KHz (~67.11 KHz SGB) 11: 16.384 KHz (~16.78 KHz SGB) 8. FF0F (IF) Name - IF Contents - Interrupt Flag (R/W) Bit 4: Transition from High to Low of Pin number P10-P13 Bit 3: Serial I/O transfer complete Bit 2: Timer Overflow Bit 1: LCDC (see STAT) Bit 0: V-Blank The priority and jump address for the above 5 by DP Page 39

Game Boy

TM

CPU Manual

2.13.1. I/O Registers

6.

FF06 (TMA)

Name

- TMA

Contents - Timer Modulo (R/W)

When the TIMA overflows, this data will

be loaded.

7.

FF07 (TAC)

Name

- TAC

Contents - Timer Control (R/W)

Bit 2 - Timer Stop

0: Stop Timer

1: Start Timer

Bits 1+0 - Input Clock Select

00: 4.096 KHz

(~4.194 KHz SGB)

01: 262.144 Khz

(~268.4 KHz SGB)

10: 65.536 KHz

(~67.11 KHz SGB)

11: 16.384 KHz

(~16.78 KHz SGB)

8.

FF0F (IF)

Name

- IF

Contents - Interrupt Flag (R/W)

Bit 4: Transition from High to Low of Pin

number P10-P13

Bit 3: Serial I/O transfer complete

Bit 2: Timer Overflow

Bit 1: LCDC (see STAT)

Bit 0: V-Blank

The priority and jump address for the above 5

by DP

Page 39