Nintendo DMG-01 Manual - Page 40

FF10 NR 10

|

View all Nintendo DMG-01 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

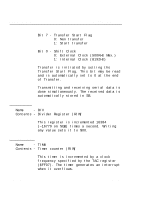

2.13.1. I/O Registers Game BoyTM CPU Manual interrupts are: Interrupt V-Blank LCDC Status Priority 1 2 Timer Overflow 3 Serial Transfer 4 Hi-Lo of P10-P13 5 Start Address $0040 $0048 - Modes 0, 1, 2 LYC=LY coincide (selectable) $0050 $0058 - when transfer is complete $0060 * When more than 1 interrupts occur at the same time only the interrupt with the highest priority can be acknowledged. When an interrupt is used a '0' should be stored in the IF register before the IE register is set. 9. FF10 (NR 10) Name - NR 10 Contents - Sound Mode 1 register, Sweep register (R/W) Bit 6-4 - Sweep Time Bit 3 - Sweep Increase/Decrease 0: Addition (frequency increases) 1: Subtraction (frequency decreases) Bit 2-0 - Number of sweep shift (n: 0-7) Sweep Time: 000: sweep off - no freq change 001: 7.8 ms (1/128Hz) 010: 15.6 ms (2/128Hz) 011: 23.4 ms (3/128Hz) Page 40 V 1.01