SanDisk SDSDH-1024 Product Manual - Page 86

Timing Diagrams

|

UPC - 710348911073

View all SanDisk SDSDH-1024 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 86 highlights

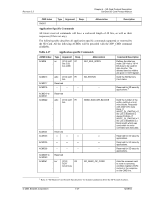

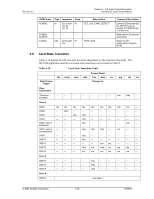

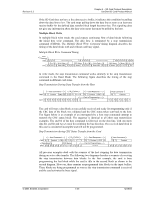

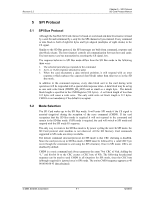

Revision 2.2 Chapter 4 - SD Card Protocol Description SanDisk SD Card Product Manual 4.10 Timing Diagrams All timing diagrams use schematics and abbreviations listed in Table 4-23. Table 4-23 Timing Diagram Symbols Symbol Definition S Start Bit (= 0) T Transmitter Bit (Host = 1, Card = 0) P One-cycle pull-up (= 1) E End Bit (= 1) Z High Impedance State (-> = 1) D Data bits X "Don't care" data bits from card * Repetition CRC Cyclic Redundancy Check Bits (7 bits) Card active Host active The difference between the P-bit and Z-bit is that a P-bit is actively driven to HIGH by the card respectively host output driver, while Z-bit is driven to (respectively kept) HIGH by the pull-up resistors RCMD respectively RDAT. Actively-driven P-bits are less sensitive to noise. All timing values are defined in Table 4-24. 4.10.1 Command and Response Card Identification and Card Operation Conditions Timing The card identification (CMD2) and card operation conditions (CMD1) timing are processed in the open-drain mode. The card response to the host command starts after exactly NID clock cycles. Identification Timing (Card ID Mode) Host Command NIDCycles CMD S T Content CRC E Z Z P *** PST CID or OCR Content ZZZ Assign a card relative address The SEND_RELATIVE_ADDR (CMD 3) for SD Card timing is given bellow. Note that CMD3 command's content, functionality and timing are different for MultiMediaCard. The minimum delay between the host command and card response is NCR clock cycles. Send Relative Address Timing Host Command NCRCycles CMD S T Content CRC E Z Z P *** Response P S T Content CRC Z E Z Z Z © 2004 SanDisk Corporation 4-42 12/08/04