Intel SL8K2 Specification Update

Intel SL8K2 - Pentium 4 3.20EGHz 800MHz 1MB Socket 478 CPU Manual

|

UPC - 683728107215

View all Intel SL8K2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Intel SL8K2 manual content summary:

- Intel SL8K2 | Specification Update - Page 1

® 4 Processor on 90 nm Process Specification Update September 2006 Notice: The Intel® Pentium® processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented - Intel SL8K2 | Specification Update - Page 2

on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. 1Hyper-Threading Technology requires a computer system with an Intel® Pentium® 4 processor supporting HT Technology and a Hyper-Threading Technology - Intel SL8K2 | Specification Update - Page 3

Contents Revision History ...4 Preface...6 Summary Tables of Changes 8 General Information ...21 Identification Information 23 Errata ...30 Specification Changes ...73 Specification Clarifications 74 Documentation Changes 75 § Intel® Pentium® 4 Processor on 90 nm Process Specification Update 3 - Intel SL8K2 | Specification Update - Page 4

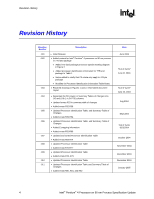

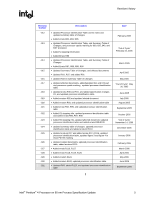

Revision History R Revision History Revision Number -001 -002 -003 Description • Initial Release • Added content for Intel® Pentium® 4 processor on 90 nm process in 775-land package • Added 775-land package processor upside marking diagram in Figure 2 • Added processor identification information - Intel SL8K2 | Specification Update - Page 5

2005 October 2005 "Out of Cycle" November 14, 2005 December 2005 January 2006 February 2006 March 2006 April 2006 May 2006 June 2006 September 2006 Intel® Pentium® 4 Processor on 90 nm Process Specification Update 5 - Intel SL8K2 | Specification Update - Page 6

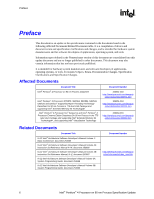

Developer's Manual Volume 3A: System Programming Guide, document 253668 IA-32 Intel Architecture Software Developer's Manual Volume 3B: System Programming Guide, document 253669 Document Number http://developer.intel.com/design/p entium4/manuals/index_new.htm 6 Intel® Pentium® 4 Processor - Intel SL8K2 | Specification Update - Page 7

the processor identification information table. Care should be taken to read all notes associated with each S-Spec number Errata are design defects or errors. Errata may cause the Intel® Pentium® processor's behavior to deviate from published specifications. Hardware and software designed to be used - Intel SL8K2 | Specification Update - Page 8

used in Intel's microprocessor Specification Updates: A = Intel® Pentium® II processor B = Mobile Intel® Pentium® II processor C = Intel® Celeron® processor D = Intel® Pentium® II Xeon® processor E = Intel® Pentium® III processor F = Intel® Pentium® processor Extreme Edition G = Intel® Pentium® III - Intel SL8K2 | Specification Update - Page 9

Summary Tables of Changes R O = Intel® Xeon® processor MP P = Intel® Xeon® processor Q = Mobile Intel® Pentium® 4 processor supporting Hyper-Threading Technology on 90-nm process technology R = Intel® Pentium® 4 processor on 90 nm process S = 64-bit Intel® Xeon® Processor with 800 MHz system bus T = - Intel SL8K2 | Specification Update - Page 10

No Fix Exception (#PF) Instead of Alignment Check Exception (#AC) on an Unlocked CMPXCHG8B Instruction R11 X X X X X X X X X No Fix FSW May Not Be SMC Detection May Cause the Processor to Hang Temporarily 10 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 11

Fix when On-Demand Clock Modulation is Enabled in a Processor Supporting Hyper- Threading Technology Memory Aliasing of Pages as R30 X Register do not Fixed Fence Pending Instruction Page Walks R35 X Fixed a System Hang Intel® Pentium® 4 Processor on 90 nm Process Specification Update 11 - Intel SL8K2 | Specification Update - Page 12

Hang R51 X IRET Instruction Performing Task Fixed Switch May Not Serialize the Processor Execution R52 X X X Incorrect Access Controls to Fixed MSR_LASTBRANCH_0_FROM_LI P MSR Registers R53 X X X X Fixed Recursive Page Walks May Cause a System Hang 12 Intel® Pentium® 4 Processor on - Intel SL8K2 | Specification Update - Page 13

Instructions May Fixed Cause #GP Fault when Descriptor is in Non-canonical Space Fixed The Base of a Null Segment May be Non-zero on a Processor Supporting Intel® Extended Memory 64 Technology (Intel in a Page-fault Exception Intel® Pentium® 4 Processor on 90 nm Process Specification Update 13 - Intel SL8K2 | Specification Update - Page 14

the IA32_EFER Register May Have an Erroneous Value For One R76 X X X Fixed Instruction Following a Mode Transition in a Hyper-Threading Enabled Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T). 14 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 15

to Cacheable Memory R85 X CPUID Instruction Incorrectly Fixed Reports CMPXCH16B as Supported Unaligned PDPTR (Page-Directory- R86 X X X X X Fixed Pointer) Base with 32-bit Mode PAE (Page Address Extension) Paging May Cause Processor to Hang Intel® Pentium® 4 Processor on 90 nm Process - Intel SL8K2 | Specification Update - Page 16

Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Fixed Compatibility Mode STOS Instructions May Alter RSI Register Results on a Processor Supporting Intel® Extended Memory 64 Technology (Intel with Slow Memory 16 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 17

Supporting Intel Fix Serviced if Instruction May Cause an Unexpected Memory Access R109 X No Fix The Execution of VMPTRLD or VMREAD May Cause an Unexpected Memory Access R110 X X X X X No Fix IRET under Certain Conditions May Cause an Unexpected Alignment Check Exception Intel® Pentium - Intel SL8K2 | Specification Update - Page 18

in VMCS May be Incorrect after a #GP on an IRET Instruction R113 VMLAUNCH/VMRESUME May Not X Plan Fail when VMCS is Programmed Pentium® 4 processor on 90 nm Process in the 478-pin package 2. Prefix "L" denotes Pentium 4 processor on 90 nm Process in the 775-land LGA package 18 Intel® Pentium - Intel SL8K2 | Specification Update - Page 19

Server/Workstation Platform configurations only. Non-server/workstation desktop configurations do not support the Intel Extended Memory 64 Technology. 4. This erratum does not apply to Pentium 4 processors for single-processor server/workstation platform configurations. 5. For these steppings, this - Intel SL8K2 | Specification Update - Page 20

Summary Tables of Changes R 20 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 21

SSPEC/Country of Assy 2-D Matrix Mark INTEL m c `03 PENTIUM® 4 X.XXGHZ / 1M / 800 SLXXX MALAY BBBBBBBB AAAAAAAA NNNN Copyright Info Product Code FPO ATPO Serial # Figure 2. Intel® Pentium® 4 Processors 570, 560, 550, 540, 530 and 520 Δ Supporting HyperThreading Technology on 90 nm Process in - Intel SL8K2 | Specification Update - Page 22

General Information R Figure 4. Intel® Pentium® 4 Processor 670, 660, 650, 640, and 630Δ on 90 nm Process in the 775-Land LGA Package Figure 5. Intel® Pentium® 4 Processor Extreme Edition on 90 nm Process in the 775-Land LGA Package § 22 Intel® Pentium® 4 Processor on 90 nm Process Specification - Intel SL8K2 | Specification Update - Page 23

EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan. Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes - Intel SL8K2 | Specification Update - Page 24

R Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes 1M 0F34h 2.80GHz/533MHz 775-land FC-LGA4 37.5 x 37.5 mm Rev 01 1, 4, 8 SL7KJ D0 1M 0F34h 2.80GHz/800MHz 775-land FC-LGA4 37.5 x 37.5 mm Rev 01 1, 4, - Intel SL8K2 | Specification Update - Page 25

Identification Information R Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes) CPUID SL7J7 D0 1M 0F34h Speed Core/Bus 3.20GHz/800MHz Package and Revision 775-land FC-LGA4 37.5 x 37.5 mm Rev 01 - Intel SL8K2 | Specification Update - Page 26

Identification Information R Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes) CPUID SL7PT E0 1M 0F41h Speed Core/Bus 2.66GHz/533MHz Package and Revision 775-land FC-LGA4 37.5 x 37.5 mm Rev 01 - Intel SL8K2 | Specification Update - Page 27

Identification Information R Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes) CPUID SL84X E0 1M 0F41h SL7Q2 E0 1M 0F41h SL7NZ E0 1M 0F41h SL8J6 E0 1M 0F41h SL82U E0 1M 0F41h SL84Y - Intel SL8K2 | Specification Update - Page 28

Identification Information R Table 1. Intel® Pentium® 4 Processor on 90 nm Process Processor Identification Information Core L2 Cache S-Spec Stepping Size (bytes) CPUID SL8PN G1 1M 0F49h Speed Core/Bus 3.06GHz/533MHz Package and Revision 775-land FC-LGA4 37.5 x 37.5 mm Rev 01 - Intel SL8K2 | Specification Update - Page 29

. 16. These parts support Enhanced Intel SpeedStep® technology. 17. These parts support Intel® Virtualization Technology 18. These parts support minimum bus ratio of 12:1 19. This SKU was produced in limited quantity and is no longer available for purchase § Intel® Pentium® 4 Processor on 90 - Intel SL8K2 | Specification Update - Page 30

not require a ModRM byte in previous generation Intel architecture processors, but does in the Pentium 4 processor. Implication: The use of an invalid Hang Due to Speculative Page Walks to Non-Existent System Memory Problem: A load operation that misses the Data Translation Lookaside Buffer ( - Intel SL8K2 | Specification Update - Page 31

UC. Since use-once does not apply to stores, the store unlock instructions go out as WB memory type. The full sequence on the bus , see the Summary Tables of Changes. R5. Problem: Machine Check Architecture Error Reporting and Recovery May Intel® Pentium® 4 Processor on 90 nm Process Specification - Intel SL8K2 | Specification Update - Page 32

SMM handler. If the SMM handler is successfully completed, it will attempt to restart the I/O instruction, but will not have the correct machine state due to the call to the MCE handler. way to determine the cause of the MCE. 32 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 33

, the Address Valid bit is incorrectly set. • The processor may hang when an instruction code fetch receives a hard failure response from the system bus. This occurs because the affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 33 - Intel SL8K2 | Specification Update - Page 34

Problem: Certain debug mechanisms may not function as expected on the processor. The cases are as follows: • When the following conditions occur: 1) An FLD instruction signals a stack overflow or underflow, 2) the FLD instruction 34 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 35

without Data Which Receive a HardFailure Response May Hang the Processor Problem: When a system bus agent (processor or chipset) issues an and then restart the faulting instruction Status: For the stepping affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm - Intel SL8K2 | Specification Update - Page 36

that the page fault handler restarts program execution at the faulting instruction after correcting the paging problem. Status: For the steppings affected, see the Summary Tables of affected, see the Summary Tables of Changes. 36 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 37

Frequencies and 12.5% STPCLK# Duty Cycle Problem: If a system de-asserts STPCLK# at a 12.5% duty cycle, the processor is running below 2 GHz, and the processor thermal control circuit affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 37 - Intel SL8K2 | Specification Update - Page 38

serviced until the interrupt enabled flag is finally set, i.e. by STI instruction Hang Problem: If Intel has not observed this erratum with any commercially available software. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 38 Intel® Pentium - Intel SL8K2 | Specification Update - Page 39

Can Cause Two Threads to Receive Stale Data and Cause Application Hang Problem: While going through a sequence of locked operations, it is possible the branch instruction. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Pentium® 4 - Intel SL8K2 | Specification Update - Page 40

HT Technology enabled system, the application may temporarily stop making forward progress. Intel has Instruction Problem: The CPUID instruction Function 80000008H (Extended Address Sizes Function) returns the address sizes supported Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 41

if data breakpoint is placed on an FP instruction. Intel has not observed this erratum with any commercially in a Hyper-Threading Technology Enabled Processor Problem: In an HT Technology enabled system, when NEM is enabled Intel® Pentium® 4 Processor on 90 nm Process Specification Update 41 - Intel SL8K2 | Specification Update - Page 42

occurs, an incorrect instruction stream may be executed resulting in unpredictable software behavior. Workaround: It is possible for the BIOS to contain a workaround for this erratum. Status: For the stepping affected, see the Summary Tables of Changes. 42 Intel® Pentium® 4 Processor on 90 - Intel SL8K2 | Specification Update - Page 43

HT Technology enabled system, it may cause a system hang. Workaround: BIOS should initialize the second thread of the processor supporting Register Do Not Fence Pending Instruction Page Walks Problem: When software writes to the Intel® Pentium® 4 Processor on 90 nm Process Specification Update 43 - Intel SL8K2 | Specification Update - Page 44

the Resume Flag (RF Flag) in a Task-State Segment (TSS) May Be Incorrect Problem: After executing a JMP instruction to the next (or other) task through a hardware task switch, it is possible see the Summary Tables of Changes. 44 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 45

since the logical processor will not be able to service any pending event. This erratum has not been Provides a 4-Byte Store Unlock after an 8-Byte Load Lock Problem: When the processor is in the Page Address Extension (PAE) Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification - Intel SL8K2 | Specification Update - Page 46

Record MSRs (LERs) Problem: The Last-Exception Record instruction and expects a fault may fail. This erratum has not been observed with commercially available software. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 46 Intel® Pentium - Intel SL8K2 | Specification Update - Page 47

: The guidelines in the IA-32 Intel® Architecture Software Developer's Manual should be followed. Status: For the steppings affected, see the Summary Tables of Changes. R45. Execution of IRET or INTn Instructions May Cause Unexpected System Behavior Problem: There is a small window of time - Intel SL8K2 | Specification Update - Page 48

Summary Tables of Changes. R51. IRET Instruction Performing Task Switch May Not Serialize the Processor Execution Problem: When an IRET instruction is executed and the NT (Nested Task , see the Summary Tables of Changes. 48 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 49

Problem: If a descriptor referenced by the selector specified for the VERR or VERW instructions is in noncanonical space, it may incorrectly cause a #GP fault on a processor supporting Intel® Extended Memory 64 Technology (Intel Intel® Pentium® 4 Processor on 90 nm Process Specification Update 49 - Intel SL8K2 | Specification Update - Page 50

Segment May Be Non-zero on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Problem: In IA-32e mode of the Intel EM64T processor, the base of a null segment may be non-zero. Implication: Due to this erratum, Intel EM64T enabled systems may encounter unexpected behavior - Intel SL8K2 | Specification Update - Page 51

RSP. Due to this erratum, this instruction fault may change the contents of RSP. This erratum has not been observed in commercially available software. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process - Intel SL8K2 | Specification Update - Page 52

a Hyper-Threading Technology Enabled Processor Problem: If the IA32_MISC_ENABLE MSR (0x1A0) C1E enable bit is not set prior to an INIT event on an HT Technology enabled system, the processor , see the Summary Tables of Changes. 52 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 53

. Checking of Page Table Base Address May Not Match the Address Bit Width Supported by the Platform Problem: If the page table base address, included in the page map level-4 table affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 53 - Intel SL8K2 | Specification Update - Page 54

Problem: In Hyper-Threading Technology enabled parts, execution of an instruction with instruction completes. Implication: A Single Step trap will be taken when not expected. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 54 Intel® Pentium - Intel SL8K2 | Specification Update - Page 55

Architecture Software Developer's Manual, Volume 3. Status: For the steppings affected, see the Summary Tables of Changes. R75. The Base of an LDT (Local Descriptor Table) Register May be Non-zero on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Problem: In IA-32e - Intel SL8K2 | Specification Update - Page 56

For One Instruction Following a Mode Transition in a Hyper-Threading Enabled Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Problem: In an Intel® EM64T enabled , see the Summary Tables of Changes. 56 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 57

affected, see the Summary Tables of Changes. R80. REP STOS/MOVS Instructions with RCX >=2^32 May Cause a System Hang Problem: In IA-32e mode using Intel EM64T-enabled processors, executing a repeating string instruction with the iteration count greater than or equal to 2^32 and a pending - Intel SL8K2 | Specification Update - Page 58

Changes. R82. An REP LODSB or an REP LODSD or an REP LODSQ Instruction with RCX >= 2^32 May Cause a System Hang on Processors Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Problem: In IA-32e mode using Intel EM64T-enabled processors, an REP LODSB or an REP LODSD or an REP LODSQ - Intel SL8K2 | Specification Update - Page 59

instruction incorrectly reports CMPXCH16B as supported Problem: A read of the CMPXCHG16B feature flag improperly indicates that the CMPXCHG16B instruction is supported. Implication: When a processor supporting Intel of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 59 - Intel SL8K2 | Specification Update - Page 60

Mode STOS Instructions May Alter RSI Register Results on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Problem: When a processor supporting Intel EM64T is , see the Summary Tables of Changes. 60 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 61

) Memory Record Problem: On a processor supporting Intel® EM64T, • If an instruction fetch wraps around Intel chipsets avoid the REQb conditions required to observe this erratum. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Pentium - Intel SL8K2 | Specification Update - Page 62

the Execution of LAHF/SAHF May Not Result in an Invalid Opcode Exception Problem: As described in the IA-32 Intel® Architecture Software Developer's Manual, support for LAHF/SAHF instructions in 64-bit mode has been added to Intel EM64T processors. The CPUID feature flag may indicate that the LAHF - Intel SL8K2 | Specification Update - Page 63

for the vector will be left set in the in-service register and mask all interrupts at the same or lower Supporting Intel® Virtualization Technology May Not Trigger Appropriate Actions Problem: When using processors supporting Intel Intel® Pentium® 4 Processor on 90 nm Process Specification - Intel SL8K2 | Specification Update - Page 64

May Cause Unexpected System Behavior Problem: In a system supporting Intel® Virtualization Technology, if INIT occurs during REP LODS/MOVS/STOS/INS/OUTS while the processor is executing in VMX guest mode, after servicing the INIT, the host will resume at the next instruction and does not complete - Intel SL8K2 | Specification Update - Page 65

a Specific Type of VM Exit Problem: In a system supporting Intel® Virtualization Technology, the processor may service a pended VM exit prior to completely by one instruction. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Pentium® 4 - Intel SL8K2 | Specification Update - Page 66

Loaded with an Unusable Segment May Cause Unexpected Memory Accesses Problem: In a system supporting Intel® EM64T and Intel® Virtualization Technology when the following occur, • The LDTR see the Summary Tables of Changes. 66 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 67

May Cause an Unexpected Memory Access Problem: On processors supporting Intel® Virtualization Technology, executing a VMPTRLD or a VMREAD instruction outside of VMX mode may result affected, see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 67 - Intel SL8K2 | Specification Update - Page 68

in VMCS May be Incorrect after a #GP on an IRET Instruction Problem: In a system supporting Intel® Virtualization Technology, the NMI blocking bit in the InterruptionInformation Field , see the Summary Tables of Changes. 68 Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 69

be erroneously Reported after an Asynchronous RESET# Assertion Problem: Machine check status MSRs may incorrectly report the are in-flight and RESET# is asserted: •Instruction Fetch Errors (IA32_MC2_STATUS with MCA error code 153) Intel® Pentium® 4 Processor on 90 nm Process Specification - Intel SL8K2 | Specification Update - Page 70

occurs due to the Guest Software executing a waiting x87 instruction after a MOVSS and the VMM injects a hardware interrupt in VM-exit Control Field Problem: Processors supporting Intel® Virtualization Technology can execute VMCALL Intel® Pentium® 4 Processor on 90 nm Process Specification Update - Intel SL8K2 | Specification Update - Page 71

memory ordering issue if multiple loads access this shared data shortly thereafter. Exposure to this problem requires the use of a data write which spans a cache line boundary. Implication: , see the Summary Tables of Changes. Intel® Pentium® 4 Processor on 90 nm Process Specification Update 71 - Intel SL8K2 | Specification Update - Page 72

MOV SS" or "POP SS" instruction is immediately followed by a hardware debugger breakpoint instruction, or • Any debug register Logical Processor from Acquiring Resources Problem: In a system supporting Hyper-Threading Technology, when 72 Intel® Pentium® 4 Processor on 90 nm Process - Intel SL8K2 | Specification Update - Page 73

The following lands have been reassigned as follows in the Intel® Pentium® 4 Processor 670, 660, 650, 640, and 630Δ and Intel® Pentium® 4 Processor Extreme Edition, Intel Pentium 4 Processor Supporting Hyper-Threading Technology, Intel Pentium 4 Processor 570/571, 560/561, 550/551, 540/541, 530 - Intel SL8K2 | Specification Update - Page 74

section apply to the following documents: • Intel® Pentium® 4 Processor 670, 660, 650, 640, and 630Δ and Intel® Pentium® 4 Processor Extreme Edition Datasheet • Intel® Pentium® 4 Processors 570/571, 560/561, 550/551, 540/541, 530/531 and 520/521Δ Supporting Hyper-Threading Technology1 Datasheet All - Intel SL8K2 | Specification Update - Page 75

® Architecture Software Developer's Manual Documentation Changes. Follow the link below to become familiar with this file. http://developer.intel.com/design/pentium4/specupdt/252046.htm There are no documentation changes in this Specification Update revision. § Intel® Pentium® 4 Processor on 90

Intel

®

Pentium

®

4 Processor on

90 nm Process

Specification Update

September 2006

R

Notice:

The Intel

®

Pentium

®

processor may contain design defects or errors known

as errata which may cause the product to deviate from published specifications.

Current characterized errata are documented in this Specification Update.

Document Number:

302352-031