Intel SL8K2 Specification Update - Page 16

Intel SL8K2 - Pentium 4 3.20EGHz 800MHz 1MB Socket 478 CPU Manual

|

UPC - 683728107215

View all Intel SL8K2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 16 highlights

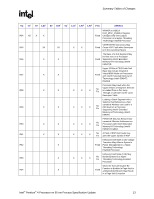

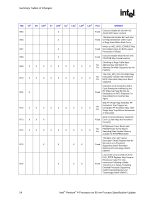

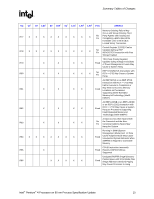

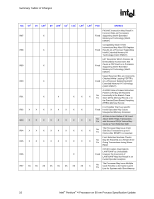

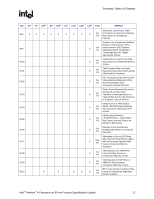

Summary Tables of Changes R NO. C01 D0 LD02 E0 LE02 G11 LG12 LN02 LR02 Plan ERRATA R87 X R88 X R89 X R90 X R91 X X X X R92 X X X X X X X X R93 X X X X X X X X R94 X X X X X X X X R95 X X X X X X X X R96 X R97 X5 X5 X5 X5 X5 X5 X5 X5 Fixed FXSAVE Instruction May Result in Incorrect Data on Processors Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Fixed Compatibility Mode STOS Instructions May Alter RSI Register Results on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Fixed LDT Descriptor Which Crosses 16 bit Boundary Access Does Not Cause a #GP Fault on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) Fixed Upper Reserved Bits are Incorrectly Checked While Loading PDPTR's on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) A 64-Bit Value of Linear Instruction Pointer (LIP) May be Reported X No Incorrectly in the Branch Trace Fix Store (BTS) Memory Record or in the Precise Event Based Sampling (PEBS) Memory Record It is Possible That Two specific Fixed Invalid Opcodes May Cause Unexpected Memory Accesses At Core-to-bus Ratios of 16:1 and X No Above Defer Reply Transactions Fix with Non-zero REQb Values May Cause a Front Side Bus Stall X No Fix The Processor May Issue Front Side Bus Transactions up to 6 Clocks after RESET# is Asserted Front Side Bus Machine Checks X No May be Reported as a Result of OnFix Going Transactions during Warm Reset Fixed CPUID Feature Flag Reports LAHF/SAHF as Unavailable however the Execution of LAHF/SAHF May Not Result in an Invalid Opcode Exception X No Fix The Processor May Issue Multiple Code Fetches to the Same Cache Line for Systems with Slow Memory 16 Intel® Pentium® 4 Processor on 90 nm Process Specification Update