Intel SL8K2 Specification Update - Page 12

Intel SL8K2 - Pentium 4 3.20EGHz 800MHz 1MB Socket 478 CPU Manual

|

UPC - 683728107215

View all Intel SL8K2 manuals

Add to My Manuals

Save this manual to your list of manuals |

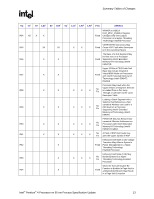

Page 12 highlights

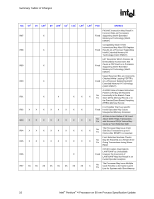

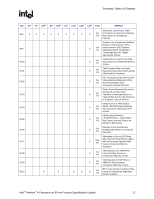

Summary Tables of Changes R NO. C01 D0 LD02 E0 LE02 G11 LG12 LN02 LR02 Plan ERRATA R38 X X X X X X X X X No Processor Provides a 4-Byte Store Fix Unlock After an 8-Byte Load Lock R39 X X X X X X X X X No Fix Data Breakpoints on the High Half of a Floating Point Line Split may not be Captured R40 X CPUID Instruction May Report Fixed Incorrect L2 Associativity in Leaf 0x80000006 R41 X Fixed The FP_ASSIST EMON Event May Return an Incorrect Count R42 X X X X X X X X X No Fix Machine Check Exceptions May not Update Last-Exception Record MSRs (LERs) R43 X X X X X X X X X No Fix MOV CR3 Performs Incorrect Reserved Bit Checking When in PAE Paging Stores to Page Tables May Not Be R44 X X X X X X X X X No Fix Visible to Pagewalks for Subsequent Loads Without Serializing or Invalidating the Page Table Entry Execution of IRET or INTn R45 X X X X X X X Fixed Instructions May Cause Unexpected System Behavior R46 X X X Fixed A Split Store Memory Access May Miss a Data Breakpoint R47 X X Fixed EFLAGS.RF May be Incorrectly Set After an IRET Instruction R48 X Read for Ownership and Fixed Simultaneous Fetch May Cause the Processor to Hang R49 X X Writing the Echo TPR Disable Bit in Fixed IA32_MISC_ENABLE May Cause a #GP Fault R50 X Fixed Cache Lock with Simultaneous Invalidate external snoop and SMC check May Cause the Processor to Hang R51 X IRET Instruction Performing Task Fixed Switch May Not Serialize the Processor Execution R52 X X X Incorrect Access Controls to Fixed MSR_LASTBRANCH_0_FROM_LI P MSR Registers R53 X X X X Fixed Recursive Page Walks May Cause a System Hang 12 Intel® Pentium® 4 Processor on 90 nm Process Specification Update