Intel SL8K2 Specification Update - Page 14

Intel SL8K2 - Pentium 4 3.20EGHz 800MHz 1MB Socket 478 CPU Manual

|

UPC - 683728107215

View all Intel SL8K2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 14 highlights

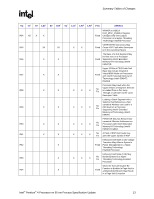

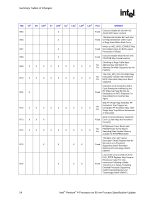

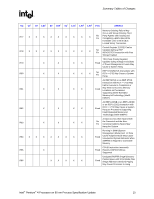

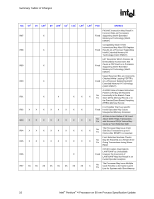

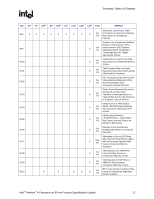

Summary Tables of Changes R NO. C01 D0 LD02 E0 LE02 G11 LG12 LN02 LR02 Plan ERRATA R65 X Fixed Execute Disable Bit Set with AD Assist Will Cause Livelock R66 X The Execute Disable Bit Fault May Fixed be Reported Before Other Types of Page Fault When Both Occur R67 X Writes to IA32_MISC_ENABLE May Fixed Not Update Flags for Both Logical Processors Threads R68 X Fixed Execute Disable Mode Bit Set with CR4.PAE May Cause Livelock Checking of Page Table Base R69 X X X X X X X X X No Address May Not Match the Fix Address Bit Width Supported by the Platform The IA32_MCi_STATUS MSR May R70 X X X X X X X X X No Improperly Indicate that Additional Fix MCA Information May Have Been Captured R71 X Fixed Execution of an Instruction with a Code Breakpoint Inhibited by the RF (Resume Flag) Bit May be Delayed by an RFO (Request For Ownership) from Another Bus Agent With TF (Trap Flag) Asserted, FP R72 X X X X X X X X X No Fix Instruction That Triggers an Unmasked FP Exception May Take Single Step Trap Before Retirement of Instruction R73 X X X MCA Corrected Memory Hierarchy Fixed Error Counter May Not Increment Correctly BTS(Branch Trace Store) and R74 X X X X X X X X X No PEBS(Precise Event Based Fix Sampling) May Update Memory outside the BTS/PEBS Buffer The Base of an LDT (Local Descriptor Table) Register May be R75 X X X X Fixed Non-zero on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) L-bit of the CS and LMA bit of the IA32_EFER Register May Have an Erroneous Value For One R76 X X X Fixed Instruction Following a Mode Transition in a Hyper-Threading Enabled Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T). 14 Intel® Pentium® 4 Processor on 90 nm Process Specification Update