Intel SL8K2 Specification Update - Page 13

Intel SL8K2 - Pentium 4 3.20EGHz 800MHz 1MB Socket 478 CPU Manual

|

UPC - 683728107215

View all Intel SL8K2 manuals

Add to My Manuals

Save this manual to your list of manuals |

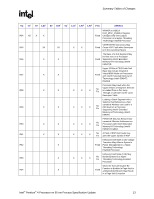

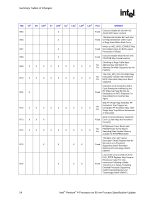

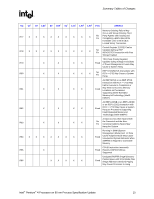

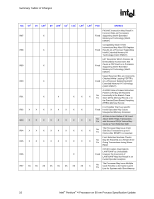

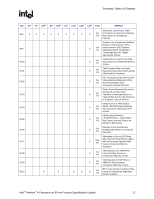

Page 13 highlights

Summary Tables of Changes R NO. C01 D0 LD02 E0 LE02 G11 LG12 LN02 LR02 Plan ERRATA R54 X5 X X R55 X5 X5 R56 X X R57 X X R58 X X R59 X X R60 X X R61 X X R62 X R63 X R64 X Fixed WRMSR to bit[0] of IA32_MISC_ENABLE Register Changes Only One Logical Processor on a Hyper-Threading Technology Enabled Processor X X VERR/VERW Instructions May Fixed Cause #GP Fault when Descriptor is in Non-canonical Space Fixed The Base of a Null Segment May be Non-zero on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T)Φ Fixed Upper 32 Bits of FS/GS with Null Base May not get Cleared in Virtual-8086 Mode on Processors with Intel® Extended Memory 64 Technology (Intel® EM64T) Enabled Processor May Fault when the X X X No Fix Upper 8 Bytes of Segment Selector is Loaded From a Far Jump Through a Call Gate via the Local Descriptor Table Loading a Stack Segment with a Selector that References a Non- X X X No Fix canonical Address can Lead to a #SS Fault on a Processor Supporting Intel® Extended Memory 64 Technology (Intel® EM64T) FXRSTOR May Not Restore Non- X X X No Fix canonical Effective Addresses on Processors with Intel® Extended Memory 64 Technology (Intel® EM64T) Enabled X X X No A Push of ESP that Faults may Fix Zero the Upper 32 Bits of RSP Fixed Enhanced Halt State (C1E) Voltage Transition May Affect a System's Power Management in a HyperThreading Technology Enabled Processor Enhanced Halt State (C1E) May X X X No Not Be Entered in a HyperFix Threading Technology Enabled Processor Fixed When the Execute Disable Bit Function is Enabled a Page-fault in a Mispredicted Branch May Result in a Page-fault Exception Intel® Pentium® 4 Processor on 90 nm Process Specification Update 13