IBM DJSA-210 Hard Drive Specifications - Page 57

Signal descriptions, Read Operation, Conventional Definition, Special Definition, for Ultra DMA

|

View all IBM DJSA-210 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 57 highlights

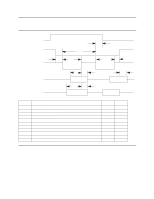

Write Operation Read Operation Special Definition (for Ultra DMA) -DDMARDY HSTROBE STOP -HDMARDY DSTROBE STOP Conventional Definition IORDY -DIOR -DIOW -DIOR IORDY -DIOW Figure 34. Special signal definitions for Ultra DMA 7.4 Signal descriptions DD00-DD15 A 16-bit bi-directional data bus between the host and the HDD. The lower 8 lines, DD00-07, are used for Register and ECC access. All 16 lines, DD00-15, are used for data transfer. These are 3-state lines with 24 mA current sink capability. DA00-DA02 These are addresses used to select the individual register in the HDD. -CS0 The chip select signal generated from the Host address bus. When active, one of the Command Block Registers [Data, Error (Features when written), Sector Count, Sector Number, Cylinder Low, Cylinder High, Drive/Head and Status (Command when written) register] can be selected. -CS1 The chip select signal generated from the Host address bus. When active, one of the Control Block Registers [Alternate Status (Device Control when written) and Drive Address register] can be selected. -RESET This line is used to reset the HDD. It shall be kept at a Low logic state during power up and kept High thereafter. -DIOW The rising edge of this signal holds data from the data bus to a register or data register of the HDD. -DIOR When this signal is low it enables data from a register or data register of the drive onto the data bus. The data on the bus shall be latched on the rising edge of -DIOR. INTRQ The interrupt is enabled only when the drive is selected and the host activates the -IEN bit in the Device Control Register. Otherwise, this signal is in high impedance state regardless of the state of the IRQ bit. The interrupt is set when the IRQ bit is set by the drive CPU. The IRQ is reset to zero by a host read of the status register or a write to the Command Register. This signal is a 3-state line with 24 mA of sink capability. Travelstar 32GH/30GT/20GN hard disk drive specifications 43