Brother International HL-720 Service Manual - Page 105

Main PCB, CPU Core, Fig. 2.3, memory space is 4 Gbytes.

|

View all Brother International HL-720 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 105 highlights

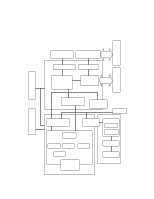

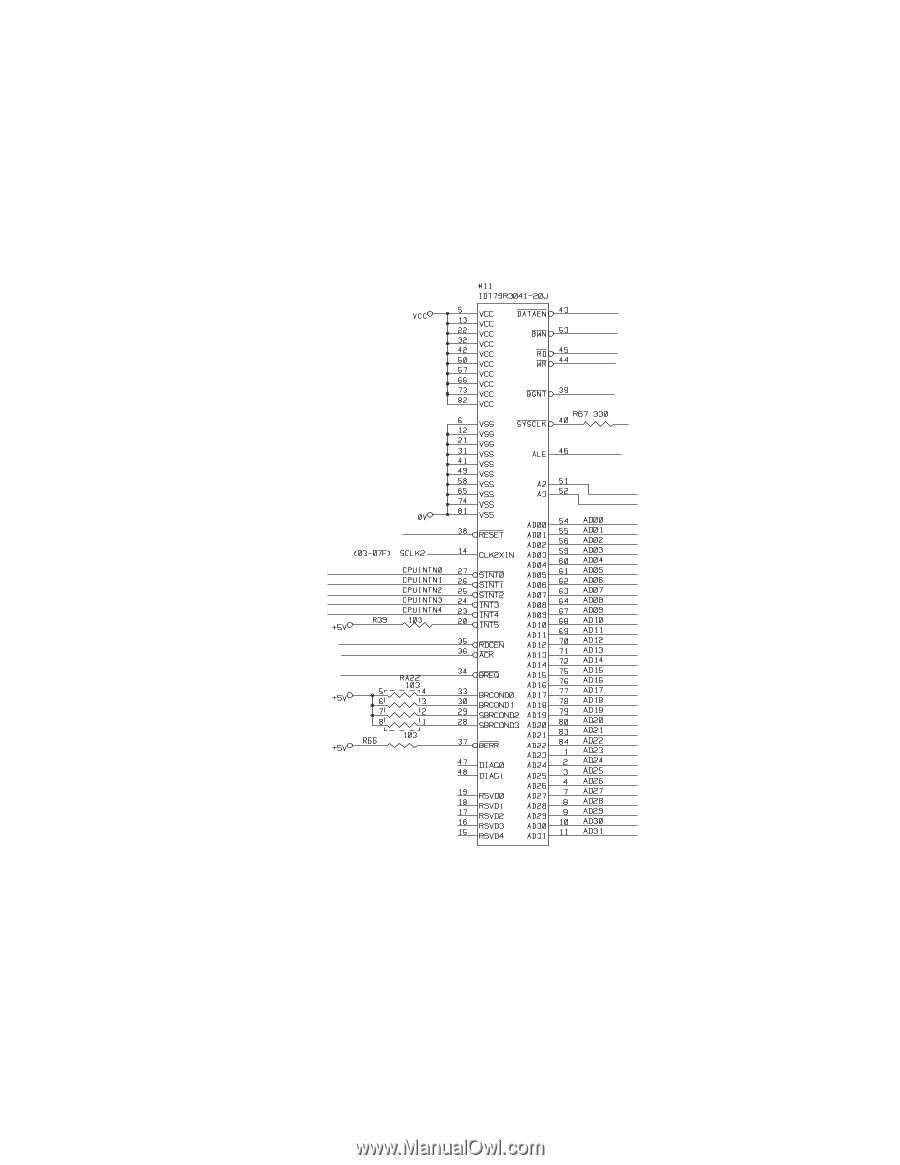

1.3 Main PCB 1.3.1 CPU Core Fig. 2.3. shows the CPU circuit block on the main PCB. The CPU is an IDT 79R3041-20J which is driven at a clock frequency of 20 MHz. This clock frequency is made by dividing the source clock of 40.0 MHz into two. The address and data bus are both 32 bit of AD0 to AD31 and D0 to D31. The total addressable memory space is 4 Gbytes. Fig. 2.3 II-3

II-3

1.3

Main PCB

1.3.1

CPU Core

Fig. 2.3. shows the CPU circuit block on the main PCB.

The CPU is an IDT 79R3041-20J which is driven at a clock frequency of 20 MHz. This

clock frequency is made by dividing the source clock of 40.0 MHz into two. The address

and data bus are both 32 bit of AD0 to AD31 and D0 to D31. The total addressable

memory space is 4 Gbytes.

Fig. 2.3