Brother International HL-720 Service Manual - Page 113

Reset Circuit, Fig. 2.10, CDCC I/O, II-11

|

View all Brother International HL-720 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 113 highlights

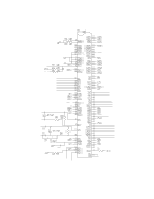

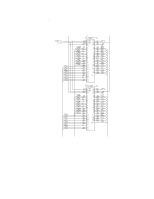

1.3.8 Reset Circuit The reset IC is PST591DMT. The reset voltage is 4.2V (typ.) and the LOW period of reset is 50 ms (typ). Fig. 2.10 1.3.9 CDCC I/O Fig. 2.11 shows the CDCC interface circuit. Fig. 2.11 II-11

II-11

1.3.8

Reset Circuit

The reset IC is PST591DMT. The reset voltage is 4.2V (typ.) and the LOW period of

reset is 50 ms (typ).

Fig. 2.10

1.3.9

CDCC I/O

Fig. 2.11 shows the CDCC interface circuit.

Fig. 2.11