Brother International HL-720 Service Manual - Page 24

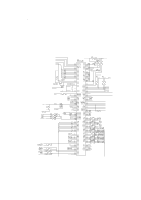

Program ROM, Working S-RAM

|

View all Brother International HL-720 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

1.3.2 ASIC The ASIC is composed of Cell Based IC and has the following function blocks. (1) Oscillator circuit Oscillator circuit drives the outside ceramic resonator, and generates the main clock for the CPU core by dividing the source clock frequency into two. It is also equipped with the several clocks for timer unit, engine control I/O unit, CDCC parallel I/O unit, data extension unit and FIFO. (2) Program ROM The program ROM of 16 Kbytes is contained in this ASIC. (3) Working S-RAM The working S-RAM of 512 Bytes is also contained in this ASIC as a work RAM for the CPU core. (4) DRAM control circuit This circuit generates the RAS, CAS, WE, OE and MA signals for the DRAM and controls the refresh for the DRAM (CAS before RAS self-refreshing method). The CPU core, the CDCC parallel I/O unit and the data extension unit access the DRAM through the DRAM bus controlled by the DRAM control unit. (5) Interrupt control This circuit controls all the interrupts to the CPU core. The CPU core has no priority to each interrupt element. If the first interrupt is accepted, then the second waits until the first has been complete. The interrupt elements can be masked respectively. (6) Timers The following timers are incorporated: Timer 1 16-bit timer Timer 2 10-bit timer Timer 3 Watch-dog timer II-7